Hi team,

My customer would like to ask two question.

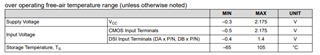

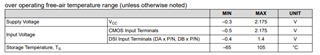

- Can we use the 2.5~3.3V external SSXO for DSI85 CLK pin? I see the max voltage is 2.175. so they can't use 2.5V to 3.3V right?

- If there any configuration about the Frequency Spread?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

My customer would like to ask two question.

1: can;'t use 2.5v

2: 25Mhz to 154Mhz.

Hi Brian,

Sorry to open this issue again.

For question 2,

My customer need confirm with us is the command or register setting that maybe need when use external SSXO?

When the IC use internal clock currently.

Do you know that, thanks.

Jason

Jason

The reference clock source is selected by HS_CLK_SRC (CSR 0x0A.0) programmed through the local I2C interface. If an external reference clock is selected, it is multiplied by the factor in REFCLK_MULTIPLIER (CSR 0x0B.1:0) to generate the FlatLink LVDS output clock. When an external reference clock is selected, it must be between 25 MHz and 154 MHz.

If the DSI channel A clock is selected, it is divided by the factor in DSI_CLK_DIVIDER (CSR 0x0B.7:3) to generate the FlatLink LVDS output clock.

Additionally, LVDS_CLK_RANGE (CSR 0x0A.3:1) and CH_DSI_CLK_RANGE(CSR 0x12) must be set to the frequency range of the FlatLink LVDS output clock and DSI Channel A input clock respectively for the internal PLL to operate correctly. After these settings are programmed, PLL_EN (CSR 0x0D.0) must be set to enable the internal PLL.

Thanks

David