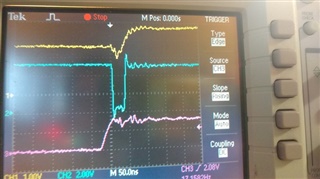

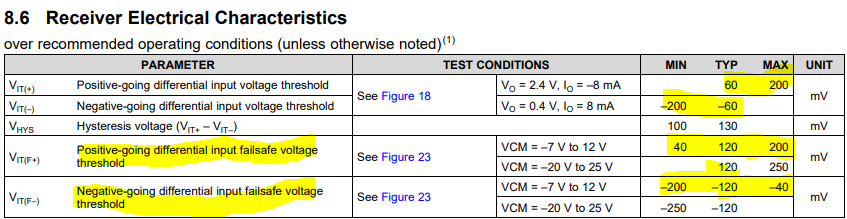

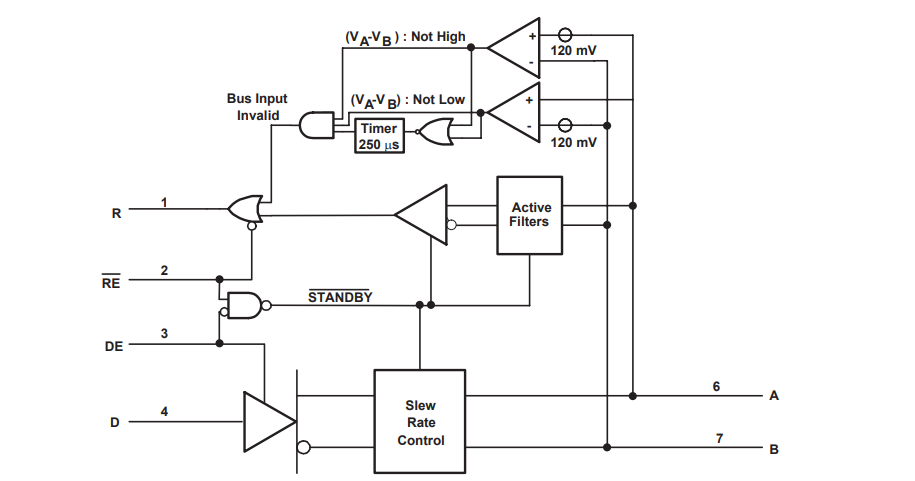

We are trying to use the SN65HVD24D in our application (in place for example of Exar XR33055 or Maxim MAX33071EASA+) but it fails due to UART errors. The speed is only 1Mbps, and the bus does have external biasing. I suspect the reason is a glitch seen on the output when Transmit enable is set high (the /ReceiveEnable is low). The glitch is short (only around 40ns) but since the UART reports noise errors, I think it is a problem.

Have you seen this glitch before?