Hi,

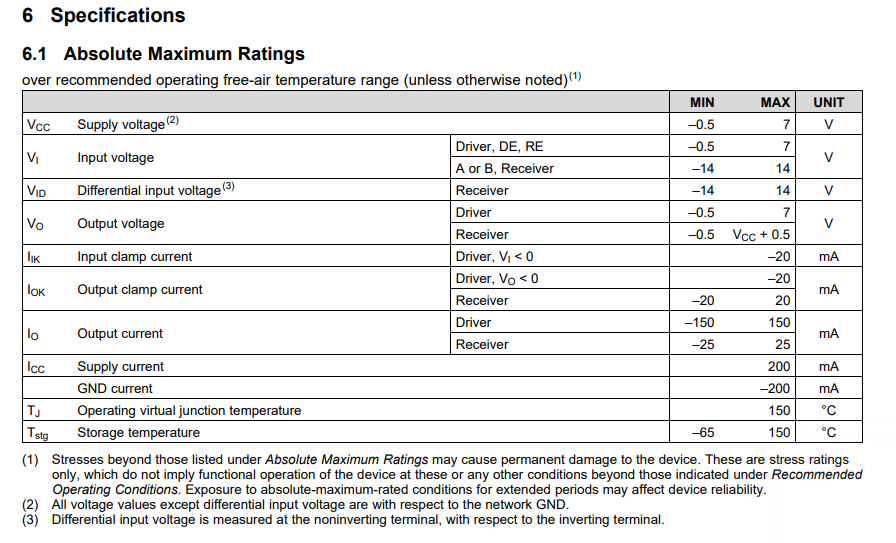

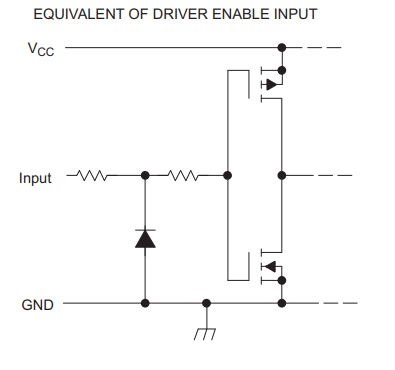

For this IC, can customer applied input voltage when there is no Vcc?

For example, 5V at input of driver before voltage is applied to Vcc. If this possible, what is the maximum input voltage is allowed, it is the same as the recommended operating condition which is 5.5V?

Thank you in advance.

Regards,

Maynard