Hi all,

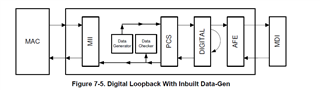

We are attempting to verify a hardware design via loopback testing. Specifically we are attempting to setup a near-end digital loopback based on information from the data sheet / forum posts.

Our System:

- Using DP83869HM transceiver

- SGMII to Copper mode

- MAC instantiated in Intel FPGA

- MAC to PHY connection is SGMII

- Running at 1gig speeds

Steps taken to setup digital loopback:

Write 0x8000 to reg 0x001F<- Performs software restart (resets PHY reg values to default)Write 0x0140 to reg 0x0000<- Sets 1000Base-T, disabled Auto-NegotiationWrite 0x5028 to reg 0x0010<- Turn off auto MDI-X, put in manual mode selecting MDI-XWrite 0xF004 to reg 0x0016<- Enable digital loopback, put PRBS in continuous modeWrite 0x4000 to reg 0x001F<- Perform software reset (preserves PHY registers values)

NOTE: We have developed some custom code to setup our PHY as per TI and Intel data sheets. This custom code executes before the above block. We have tested both with and without this custom code.

Steps taken to verify loopback is working / non-working:

- Examine reg 0x001 (BMSR), looking for LINK_STS1 to be 1 (link up)

- This was suggested by another forum post found here: e2e.ti.com/.../3888709

- Examine reg 0x0039 (PRBS_TX_CHK_CTRL), looking for any number of error bytes

- Examine reg 0x003A (PRBS_TX_CHK_BYTE_CNT), looking for any number of error bytes

In all cases, the link status (LINK_STS1) is down

In all cases, PRBS_TX_CHK_CTRL and PRBS_TX_CHK_BYTE_CNT registers were 0

So my questions at this point are:

- Are the steps listed above for setting digital loopback correct? Is there something we're missing?

- Are there other ways to verify if digital loopback is working?

Below is a register dump from a run in which we attempted to setup digital loopback. Note that the BMSR below indicates that the PHY link is not up, and both PRBS registers indicate 0 (error or correct) bytes received.