hello their,

customer is working on external crystal design for dp83tg720s-Q1.

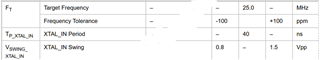

however, on the datasheet, I don't find the voltage requirement for XI pin.

would you please share the voltage requirements of dp83tg720s-Q1's XI pin, like the image shown below.

BRs,

Shubiao Wang