Hi Team,

I'm FAE support Lenovo LCFC, now customer wants to use our SN65DPHY440SS as MIPI DPHY retimer. Could you please help with below application related questions? Appreciate for your support and help.

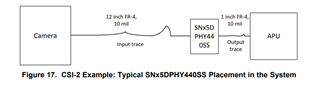

1. Our "Typical SN65DPHY440SS Placement in the System" shows a 12 inch FR-4 is recommended as input trace, but actually customer has a 20 inch long input trace. Would one piece of SN65DPHY440SS could support that 20 inch input trace distance? if not, does customer need two pieces of SN65DPHY440SS to support this application?

2. Our layout guidelines show "DAxP/N and DB*P/N pairs should be routed with controlled 100-Ω differential impedance (± 15%) or 50-Ω single-ended impedance (± 15%).", which is different from the MIPI DPHY LP Transmitter interface Electrical characteristics "Minimum value 110 Ω". Which parameter should be referred to?

3. SN65DPHY440SS supports up to 4 lanes at 1.5 Gbps, does it can support 4K camera? How to calculate the relation between the camera resolution and lanes speed?

Best Regards

Steven Yuan