Hi,

I'm working on a case and generating color bar on TI DS90UB954, and passing through CSI-2x4lanes to a SOC.

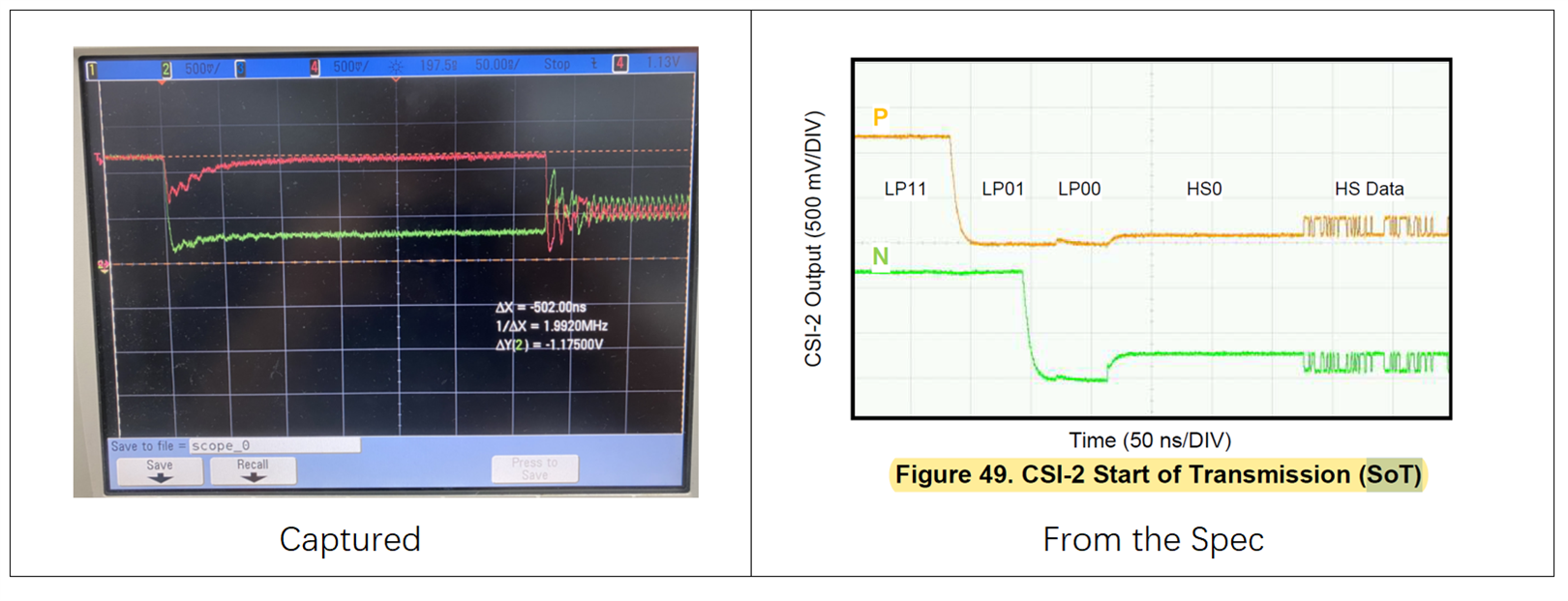

Since the SOC can not detect the SOT, I get the below capture from one of the data lane pairs. (Actually all 4lanes look the same.)

I can see it's way different from the 954 spec, but having no idea what I'm doing wrong.

I've checked the power supplies and they look correct.

Can you help to give some advice on what's the possible cause or what should I do? Thanks,

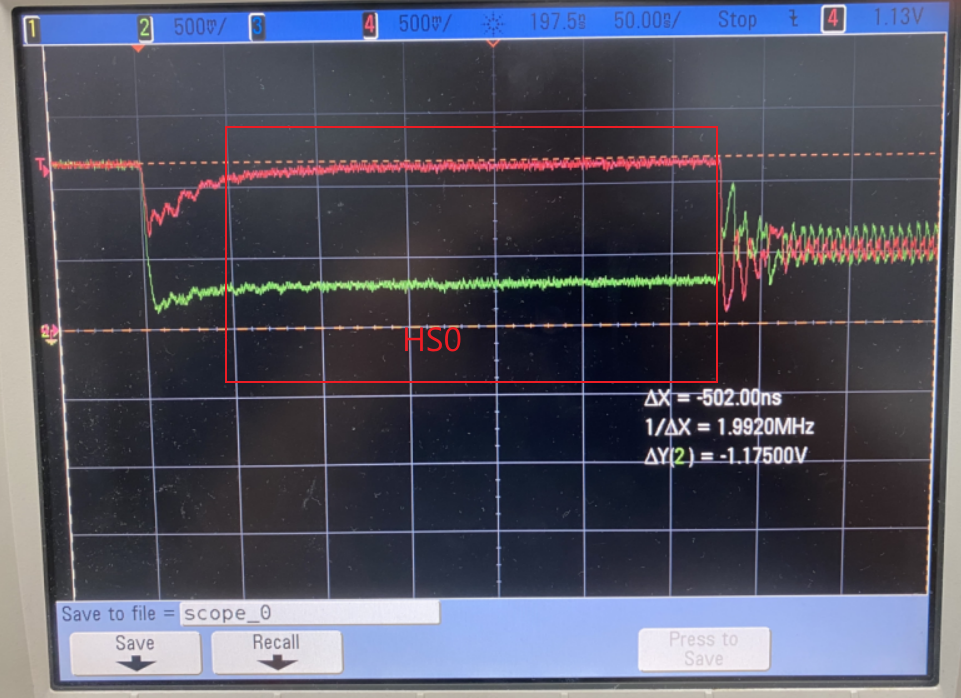

And while I'm changing the CSI0_THS_ZERO register, below part is changing and that points out the HS0 field. But when I'm changing other time related registers of CSI0, nothing happen.

Thank you!