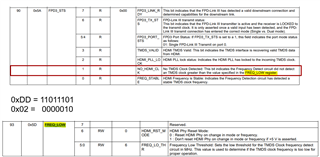

I have issue with multiple boards in a know good design (we have built hundreds that work). We are not getting link to our display and the output of register 0x5A is 0x02. On a working board the result is 0xDD.

This bit implies we are not getting a clock in from the HDMI interface, but I did verify we were seeing a clock at the pins of the 929. Could it mean something else?

Here is the entire register dump from the 929:

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 18 00 00 da 80 00 00 c0 c0 00 00 00 00 22 22 02 ?..??..??....""?

10: 22 00 00 e8 00 00 fe 1e 7f 7f 01 00 00 00 01 00 "..?..?????...?.

20: 00 00 25 00 00 00 00 00 01 20 20 e0 00 00 a5 5a ..%.....? ?..?Z

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 14 5c 00 00 80 00 00 00 00 00 00 00 00 00 00 00 ?\..?...........

50: 97 a1 1e 00 0c 0c 00 00 00 00 02 a0 02 06 44 00 ???.??....????D.

60: 22 02 00 00 10 00 00 00 00 00 00 00 00 00 00 00 "?..?...........

70: c2 c4 c6 82 7c 5a 00 c2 c4 c6 82 7c 5a 00 00 00 ????|Z.????|Z...

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 a8 00 40 00 00 00 c0 00 00 00 00 00 ff 00 ..?.@...?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 a8 00 40 38 00 00 00 00 00 00 00 00 00 00 ..?.@8..........

f0: 5f 55 42 39 32 39 00 00 00 00 00 00 00 00 00 00 _UB929..........