Other Parts Discussed in Thread: DSI-TUNER

Hello TI Experts,

I have seen the FAQ on how to configure the SN65DSI84 with DSI-Tuner. I have tried to configure the SN65DSI84 with single 4-lane DSI / Dual LVDS for our 1280x1024p@60fps display but i have some remaining questions.

As far as I understand, our DSI clock frequency is fixed as the datasheet of the SOM connected to the SN65 DSI input specifies a frequency of 1.5 Gbps per lane. I am not sure what value to put in DSI-Tuner as DSI Ch A CLK. All my attempts seemed to result in incompatible values in the output tab.

Could you tell me how exactly I can compute the correct DSI CLK frequency from the 1.5 Gbps per lane value ?

The relevant documentation for our LVDS and DSI characteristics are as follows.

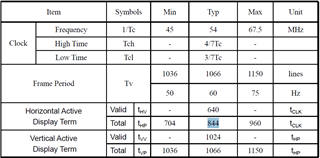

Our screen timings :

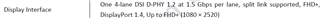

DSI interface from our SOM:

Thank you in advance for your answer,

Best Regards

Glenn