Dear Team,

Question 1:

Below is the I2C wave from captured .You can see that the ACK is coming to 0.8V.May I know is this due to the presence of level shifter.

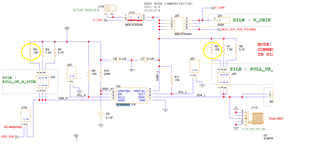

Please see my circuit below.The pull up used is 10K,LOW side voltage is 2.9V and HIGH side voltage is 5V.

Qusetion2:

You can see that two acknowledgements are coming (Yellow Circle).

After that you can see that there is no ACK and SDA pulled to LOW and SCL pulled to high.

No clock is coming after that.May I know is it an expected behaviour.I mean clock properly comes from Arduino only when it receives ACK properly.

Question 3:

Looking closely at trace(1st image), it appears that SDA is transitioning low-to-high while SCL is low. This appears to be the controller sending the STOP condition, in the middle of a frame.

Is this a firmware issue