Hi Team,

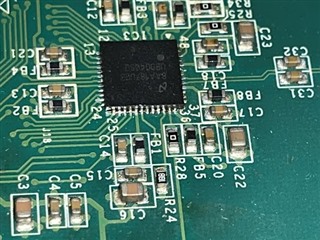

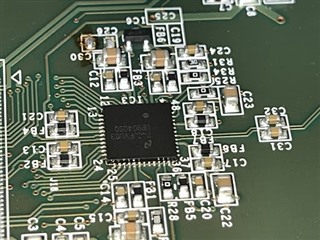

Our customer encountered a problem with some batch of DS90UB904Q and would like to ask some diagnostic test to determine the causes the device to "reset"/loose PLL lock. Please see the details of his inquiry below.

We have an issue with DS90UB904Q PLL not locking. What could the issue be, any reported batch issue or other things as we only have this problem on some batches

Batch starting with 8aa1 works. Batch starting with 97ae does not work

We have confirmed that the board is not the issue by switching between IC batches on the same board.

Good 8aa1 was bought from Digikey. Bad 97ae was bought by our EMS from rochester

Can you suggest things for me to test meanwhile? To find if it's a tolerance issue on the board.

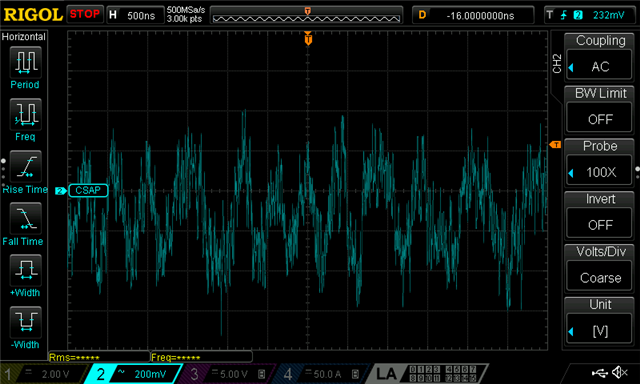

So PLL is not locking on bad boards. The LOCK output is going LOW many times and we loose the picture on the display when it happens.

What causes the chip to "reset"/loose PLL lock?

Regards,

Danilo