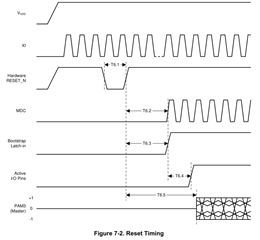

In DP83TG720R-Q1 datasheet, it has defined the below reset Timing:

we have below questions:

a) Does the VDD contain all the power supplies of VDDA VDDIO VDD1P0 in the figure?

b) VDDA VDDIO VDD1P0 power supply which module of Phy IC? If VDDA and VDDIO come up first, VDD1P0 comes up later, or MCU reset causing VDD1P0 voltage be lowered and then raised, which will have an impact on the establishment of Ethernet communication?

c) What is the specific function of Bootstrap Latch-in? Does it control by STRIP_1 Pin (14th Pin of the Phy IC)?

d) If DP83TG720 first initialization fails, does the Phy chip can support retry initialization again? if yes, how to config it when retry it again?

e) During the power up Timing, Does the Hardware Reset_ N Pin also need to be config By MCU SW in the same way as Reset Timing?