Hi team,

1、Does the chip DP83TG720SWCST Q1 need at least two external power supplies, 3.3V and 1.0V?Does the chip DP83TG720SWCST Q1 need at least two external power supplies, 3.3V and 1.0V? Is there no power-up sequence requirement?

...

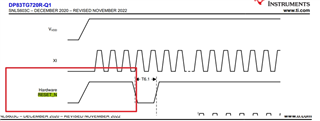

2、Is there any requirement for the time from 3.3V and 1.0V to reset release? Or does the reset pin need to be pulled high when the power is first turned on?

3.、Are there timing requirements for VDDIO, VDD1P0, VDDA, and VSLEEP?

4.、Do the reset signals of VDDIO, VDD1P0, VDDA, and VSLEEP need to be pulled high all the time during the power-on phase? Or pull low first and then pull high? Or is it pulled high first, then pulled low, and then pulled high again?