HI,Team

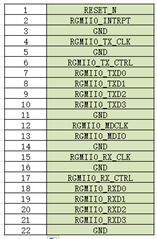

Regarding the RGMII signals of DP83867IRRGZT, they include TX_CLK, TX_D[3:0], RX_CLK, RX_D[3:0], TX_CTRL, RX_CTRL, MDC, MDIO, INT_PWDN, RESET_N. What are the signal spacing requirements in PCB LAYOUT? If grouped according to read and write, MDC, MDIO, INT_PWDN, RESET_N, can they be assigned to the read group or write group? Or a separate group?Thank you so much.