I submitted a techsupt request and was told instead to post here. That'd better mean that TI reps actually answer *here* if they don't answer directly...

I have a product under development that needs to find the right RS-485 transceiver. The original attempt was the MAX13451, but that either put too much load on the bus or doesn't drive strong enough, resulting in sagging and ringing on every transition and a very restrictive limit of how many units could be on the bus.

The SN65HVD24 was looking better until I hooked up the bus backwards (an absolute requirement of the design). The receive output went from perfectly clean and viable to quite shredded, even though the A and B signals were just swapped.

Some background: the units connect to the bus for both inductively-coupled power and capacitively-coupled data. The bus has 36V DC plus the RS-485 signal. The SN65HVD24 is run from 5.5V and interfaces to a 3.3V microcontroller with a series resistor on the receive line.

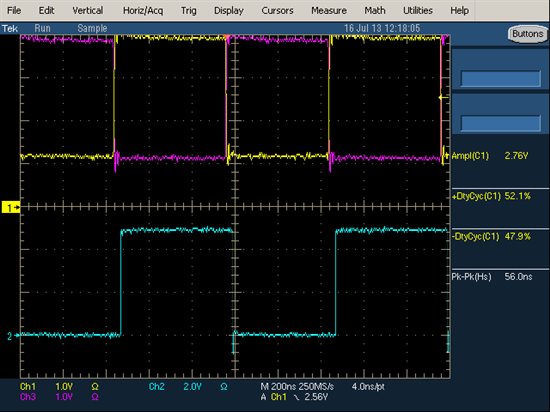

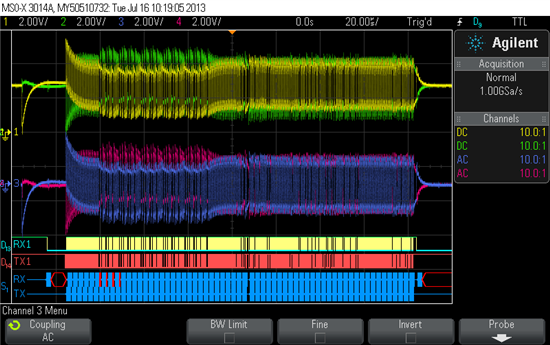

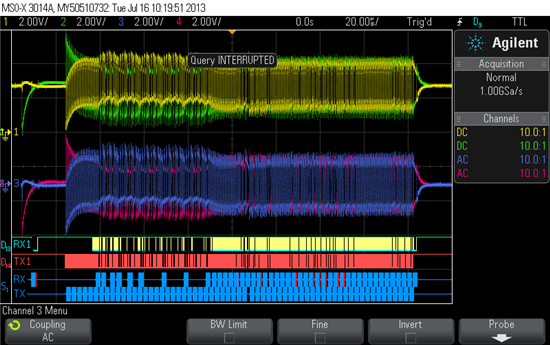

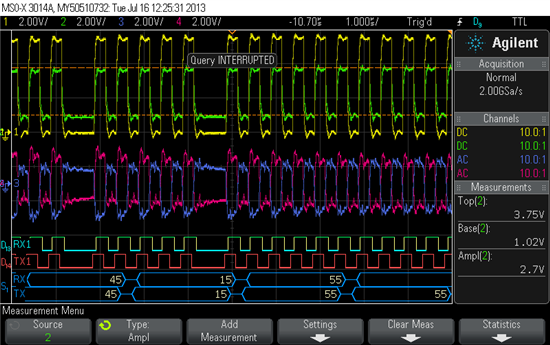

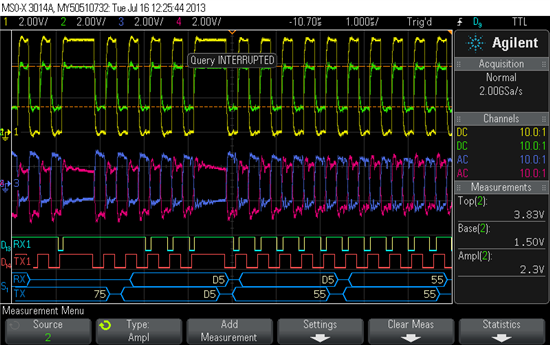

In the attached image are 3 tests. The top shows a viable packet being sent, with yellow and green being probed between the capacitive coupling and the HVD24 (DC coupled probes, ground to the test board, signal clearly centered at 5.5v/2), while the digital signal is an isolated (ADuM, part of my test/program fixture) copy of the received signal output by the HVD24 through the series resistor into the microcontroller. The middle image shows what happens when I reverse the A and B lines. Instead of a viable receive signal it gets completely lost during the preamble and is almost never comprehensible after that.

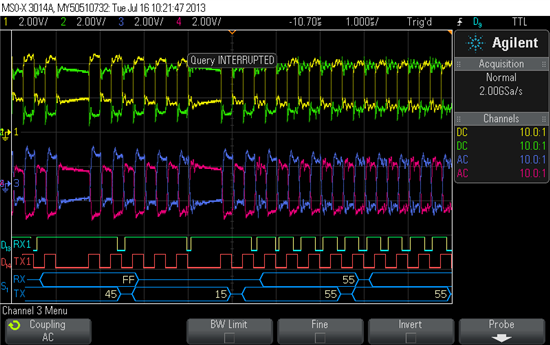

The preamble (left of T0) is:

0x55 (x5) [condition/center bus]

0x44 0x11 0x45 0x15 (x5) [resync UART receive statemachine]

0x55 (x5) [recenter]

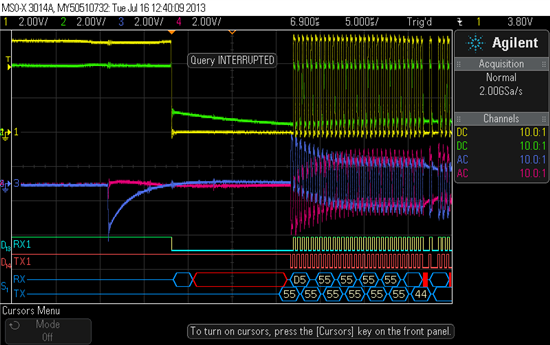

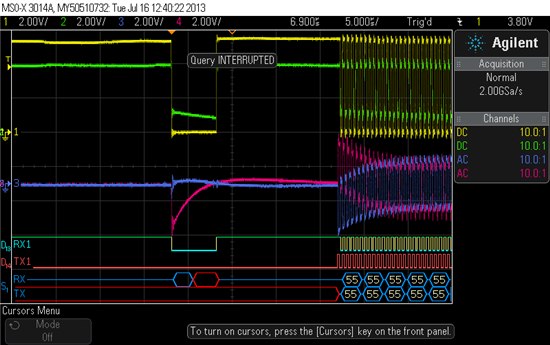

The bottom shot shows what happens when I double the preamble all the way around. The signal still gets lost immediately in the resync section,but comes back in time for the data packet. This results in a slightly higher successful reception rate (maybe 20% instead of 10%).

My understanding of RS-485 is that this should absolutely not be happening. The input signal is clearly within range (they idle at the same voltage, halfway up VCC), so swapping the signals should have no effect other than inverting the output.

I have tried several chips and gotten the same result, though I can work through a few more if there's any chance that particular chips are bad. As it stands though, I just sent out for boards to hold the MAX3292, which may be a better fit anyway because of the transmit pre-emphasis.