I have a design between an SMT32F4 and a DP83848T that has been used on a half-dozen boards with various layouts. I have had no problems.

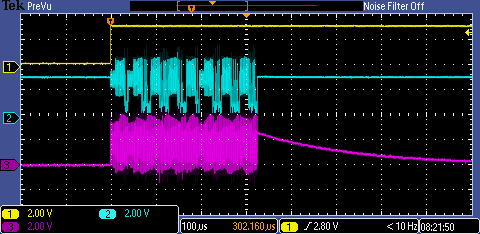

I recently had ten boards built using this core design and nine of the ten have no problems. On one of these boards the Phy produces TX_CLK for 330 usec and then an exponential decay to zero. After 30 seconds of waiting for the Phy to respond, the microcontroller holds the Phy reset line low for 650msec. When the reset line is released, TX_CLK again goes active for 330usec and again, the exponential decay. The scope trances are identical each time. This process continues until eventually (several cycles to 20 minutes) the TX_CLK line goes active and stays active, the microcontroller is happy and every thing is fine until the next power cycle.

The 25MHz crystal signal appears fine as is the 25MHz Out signal (Pin 21) throughout this whole process. Resistance to ground and voltage levels on all of the pins between this board and the others that work are identical.

I am at a loss. Before I replace the chip (WQFN), I was wondering if anyone may have suggestions that I may have over looked.

Thanks.