Other Parts Discussed in Thread: SN65DSI85

Hi,

I would like you to confirm whether following usecase can be acceptable or not.

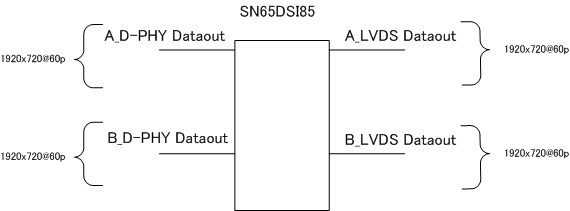

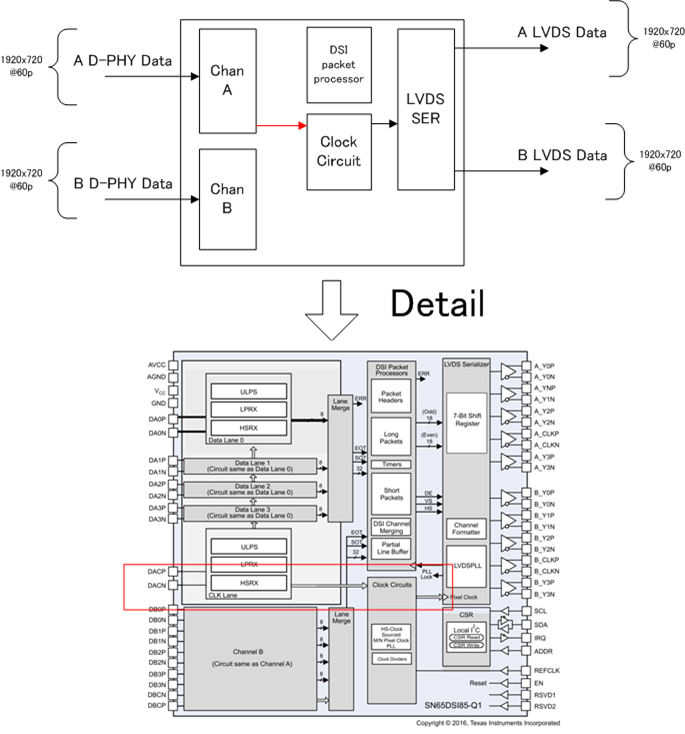

* Two input at 1920x720@60 and two output.

According to datasheet, it seems that up to 154MHz is limitation in case of Dual link.

So above usecase can be acceptable.

However, I would like you to confirm that my understanding is correct just in case.

So could you confirm whether my understanding is correct or not ?

Best Regards,

Machida