Hi,

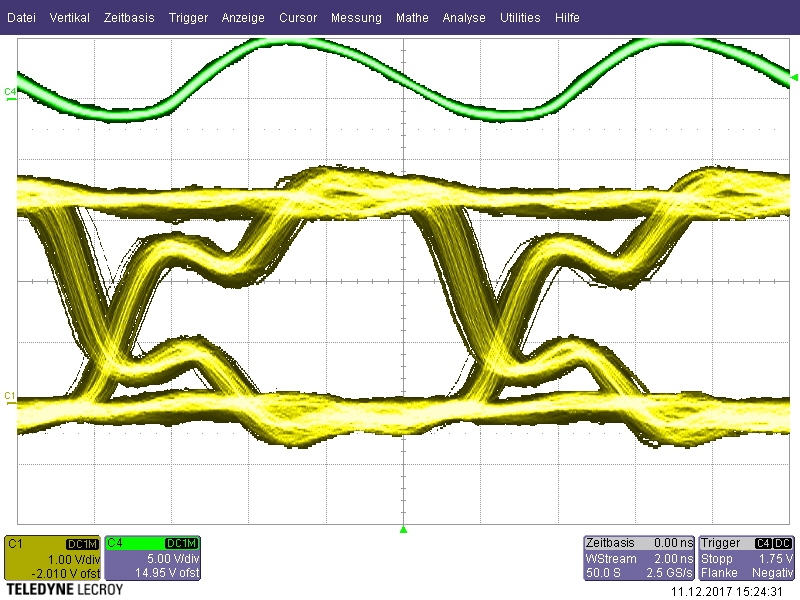

We have an application where we want to transmit data with up to 100Mbit/s with LVDS technology. Therefore we have chosen the SN65LVDT388A device. With a test board that connects the pin 35 (A1Y) to a Xilinx Artix-7 (AC701 board) we tested the signal integrity @ 100Mbit/s. Unfortunately the rising and falling edges do not look very promising. Please see attached eye diagram CH1 (yellow signal). When I leave the output of the SN65LVDT388A open, the signal looks perfect. The input pin of the Xilinx Artix-7 is configured for LVTTL with 3.3V.

The distance between the SN65LVDT388A and the FPGA is about 8 inch. Any idea what could be the problem? Is it possible that reflections can lead to a signal like this?

Thanks and best regards,

Patrick

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.