Other Parts Discussed in Thread: DS90LV001

By the way, does anyone know what exactly EN pin does?

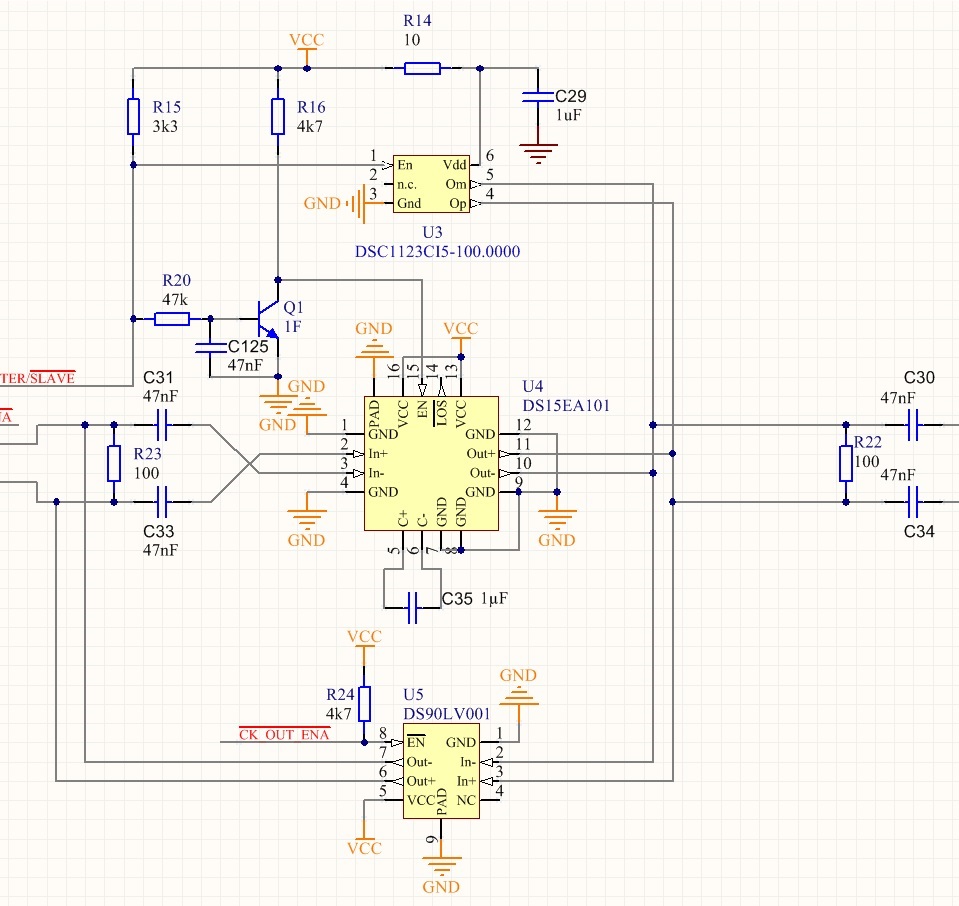

Have 2 lvds clocks electrically paralleled (=wire or'ed), one from a DSC1123 100MHz mems oscillator, and the other from an incoming diff pair.

The latter gets equalized by this DS15EA101, when available and selected.

For selection, I do manage the EN pins for these two devices in order to change the source available on common output lines.

The strange i see is a low frequency on/off pattern superimposed on the 100Mhz clock. It varies in frequency as i do probe or touch the equalizer external capacitor at pins 5&6.

But EN is low! should'nt it disable the outputs, hence any influence of the ds15101 on it's outputs?

And, will the 50 ohm internall pull-up terminators stay there also when disabled?

Thanks for your help!

Francesco