Other Parts Discussed in Thread: TL16C550C, SN54LS674

Hello,

I ordered a few mpc2221 chips from Microchip. It is a small chip that is capable of converting usb signal to vitual RS232 signals. I also ordered some leds from Vishay and ... The TIR1000 from TI. So far so good. Now is the question. How can i make that pic generating the 16XCLK baud clocking signal i need??? Wel after some thinking and reading i found out the pic is capable ( running internaly on 12Mhz ) to output his clock signal !!! 12Mhz normal, can be doubled by a PLL to 24Mhz.

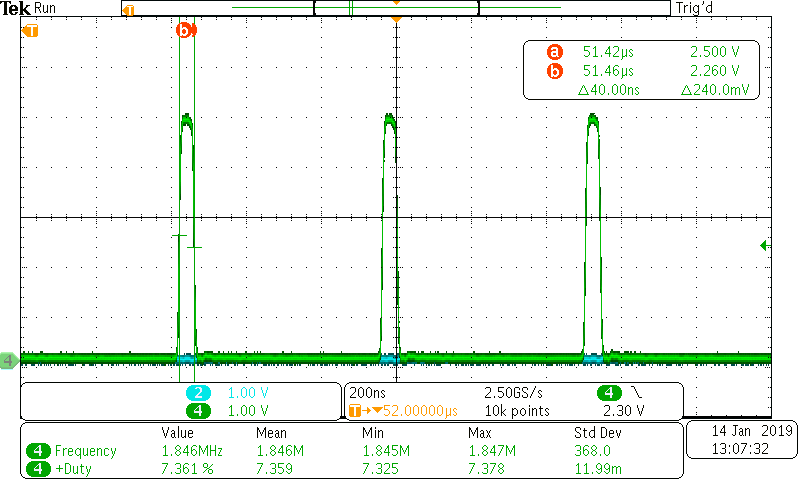

So I was thinking ... If i could use that pic output signal and divide it as it should i might somehow meet up with 1.843 MHz to drive the 16Xclk clock instead of the standard available 1,5MHz ??? Now 12 / 1,8 = 6,5. way off. BUT in PLLx2 mode. 24Mh (0,5% error rate maximum as 12Mhz is calibrated to 0,25% ) / 13 = 1,846153846153846 !!!!!!! I came to the conclusion 24MHz / 13 gives a 1,6% error rate on the 115K and 38K baudrate. But sadly ... We cannot program that pic with our own code. Just enable and set the INTclk out divider.

Now here it comes !!! Why not using a dedicated 14 bit counter ??? let us say the "74hc4060" We connect the reset line to Q13 and CLKin to the pic's 24MHz output clock. Et voila there we go.

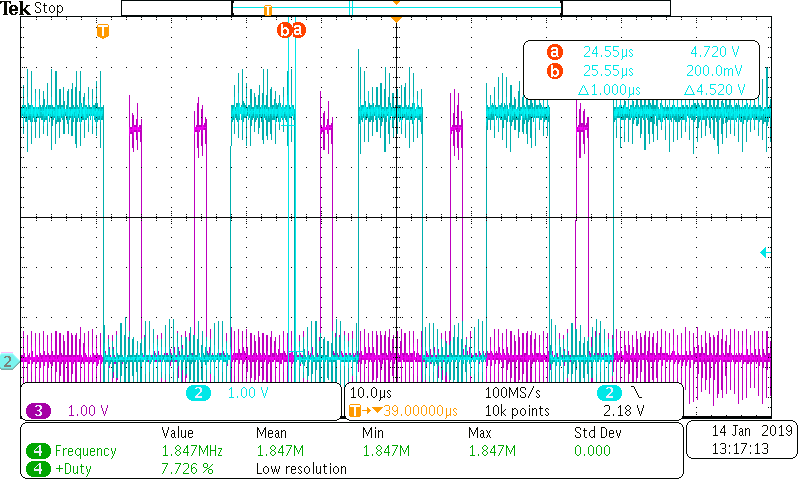

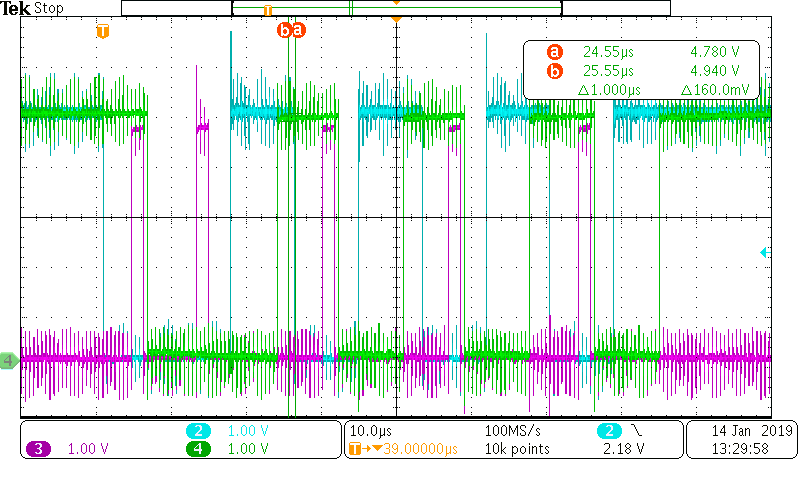

My question is. That pulsetrain wil be in pwm 1/13 instead of 50/50. So the Hz's are then nearly perfect. But duty cycle has dropped to 7,7%.

1st Question Is: that an issue?

2nd Question. Will this work?