Hello,

my customer has some problem using SN65MLVD201D.

They use these components to control transfer data on a BUS ( using T-BUS of phoenix Contact of what we don’t have specification ).The first step is to have a front end with a maximum of 8 modules connected in the configuration.

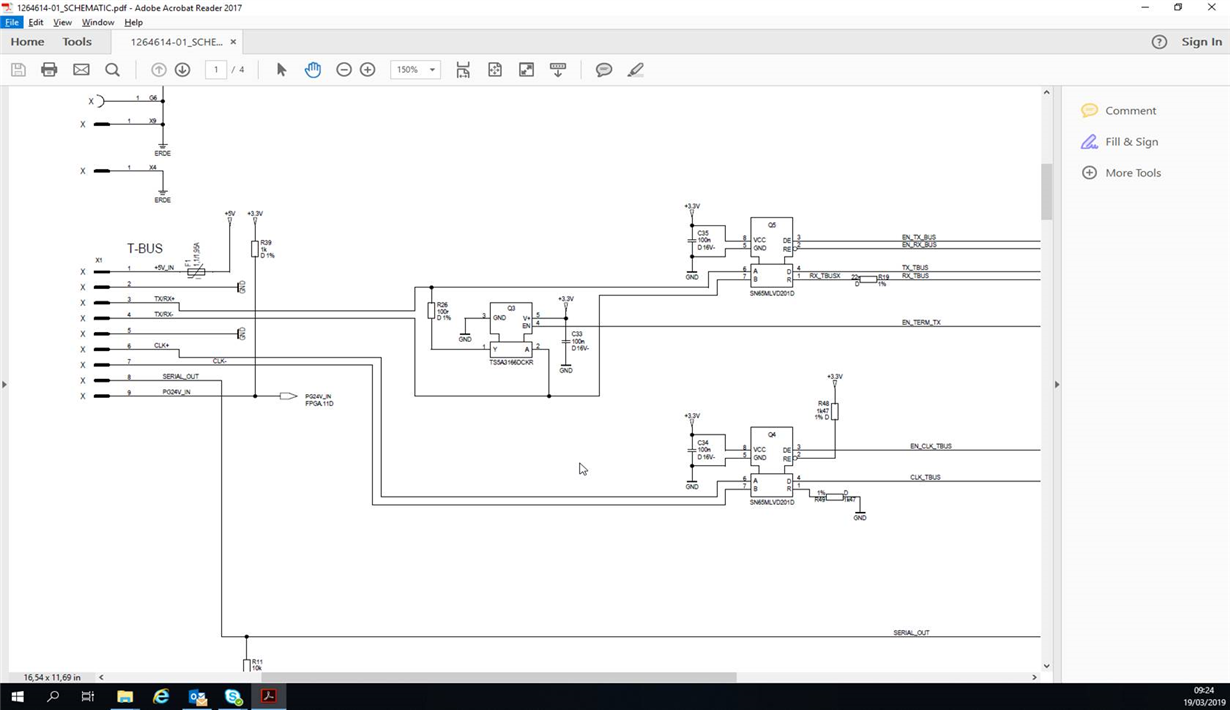

Here in attached part of the schematic of the FRONT END

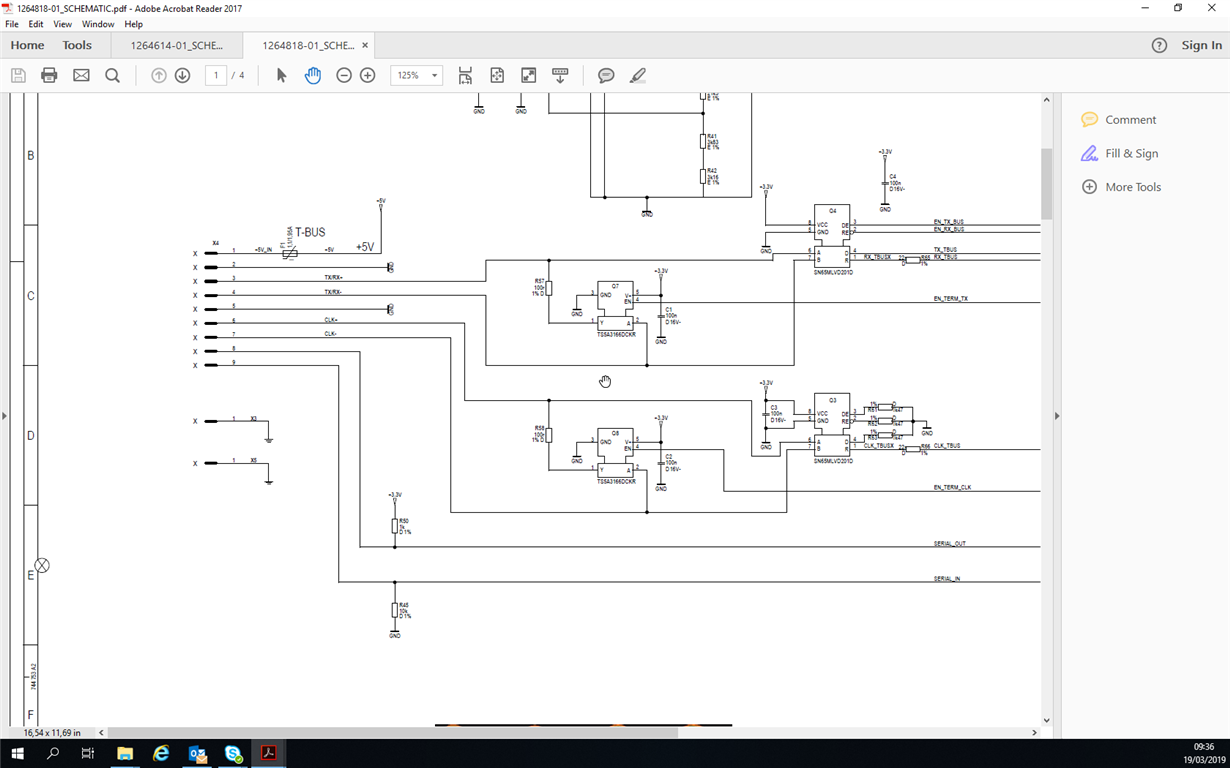

Here in attached part of the schematic of other modules

Notes :

The clk+ clk- is only in one direction from front end to the modules . The frequency now is about 25 Mhz

The tx/rx+ tx/rx- signal are in both direction controlled by some state machine in FPGA in Front end and modules .

In the front end the resistor R26 100 ohm is always enabled

In the module only the last , the R58 and R57 resistors ( 100 ohm ) are enabled .

They have problem of some oscillation after about 6 modules .

Do you think is necessary to add some voltage levels fixed by partition resistor on tx/rx+ tx/rx- signal preventing some strange

Level during transition from TX to RX ?

Please have a look to the schematic and tell me if there is any doubt or suggestion.

Regards,

Stani