Dear team,

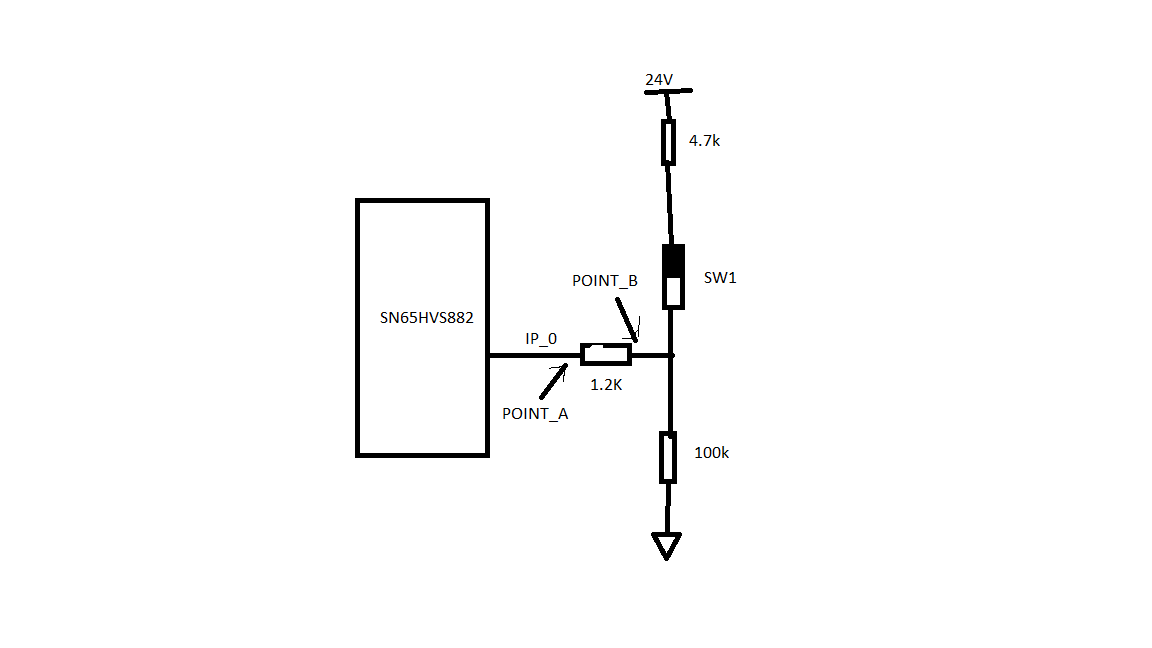

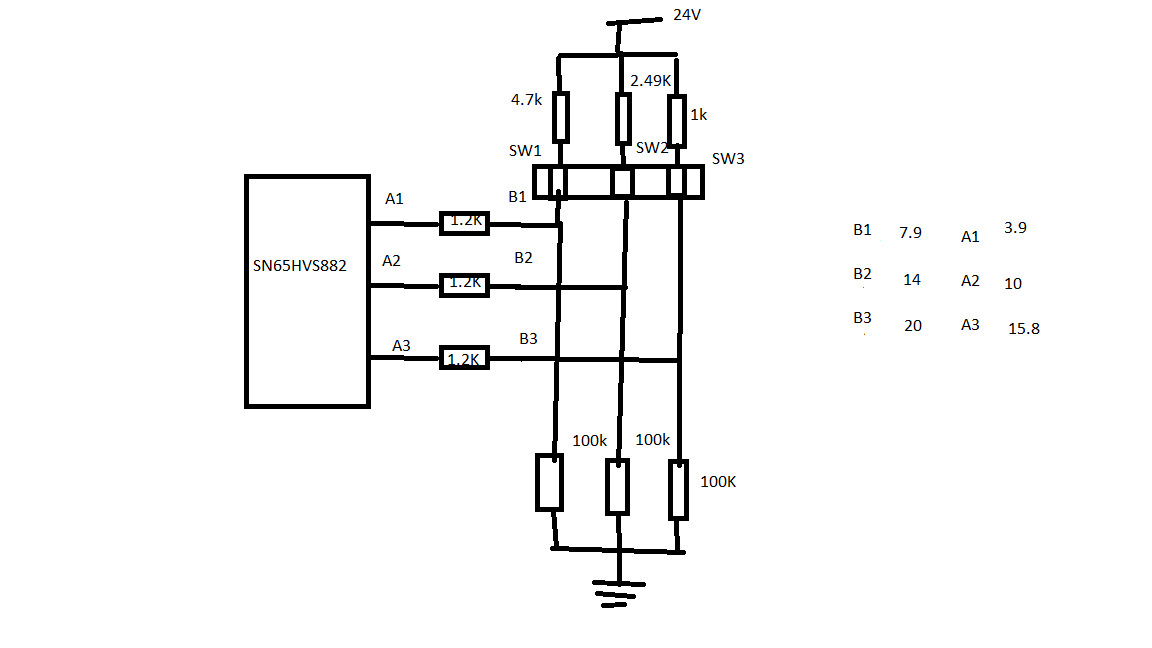

We are using this IC to read data from sensors. we have made testjig where we are feeding 8 digital inputs which is of 24V level to SERIALIZER and we are reading it from SOC. Right now we are only able to read it first time, if we change the input to serializer which is some other value we are not able to read it, But if we again power on and of then we are able to read the proper data.

what is the reason for this.