Other Parts Discussed in Thread: DS110DF111, LMX2595, LMX2595EVM, DS110DF410EVM

Hello,

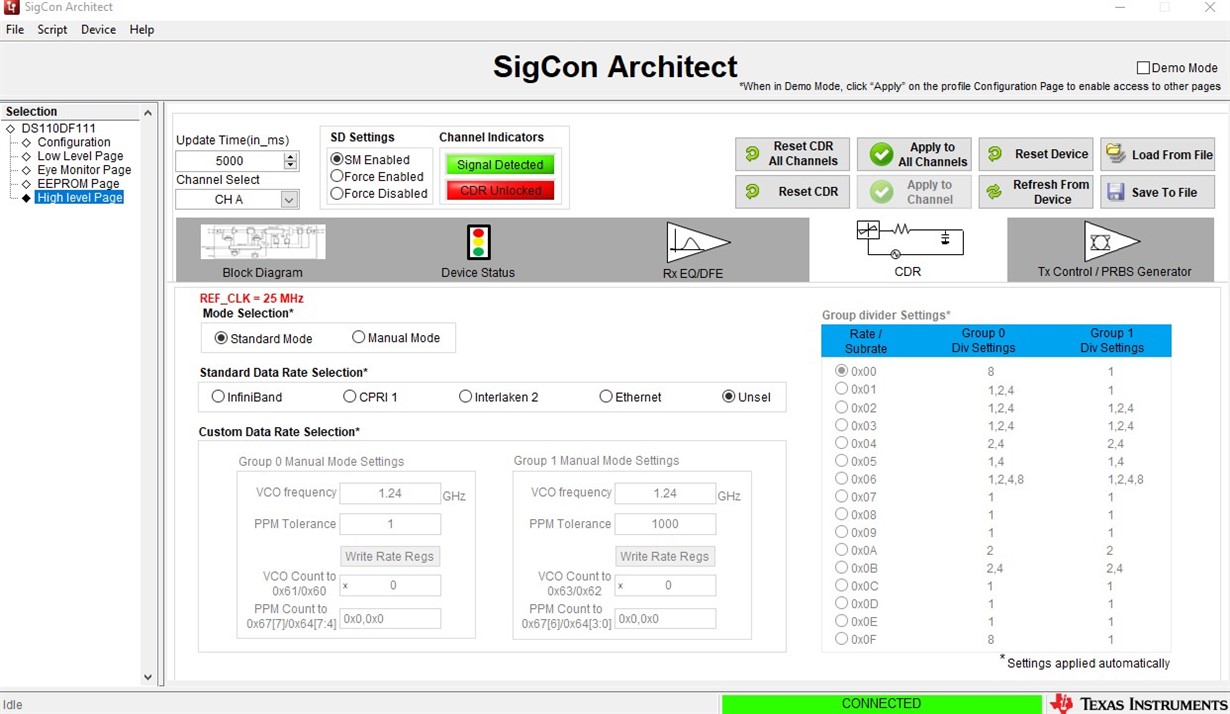

I'm using a DS110DF111 evaluation board to generate PRBS signal on a 1 GHz input signal.

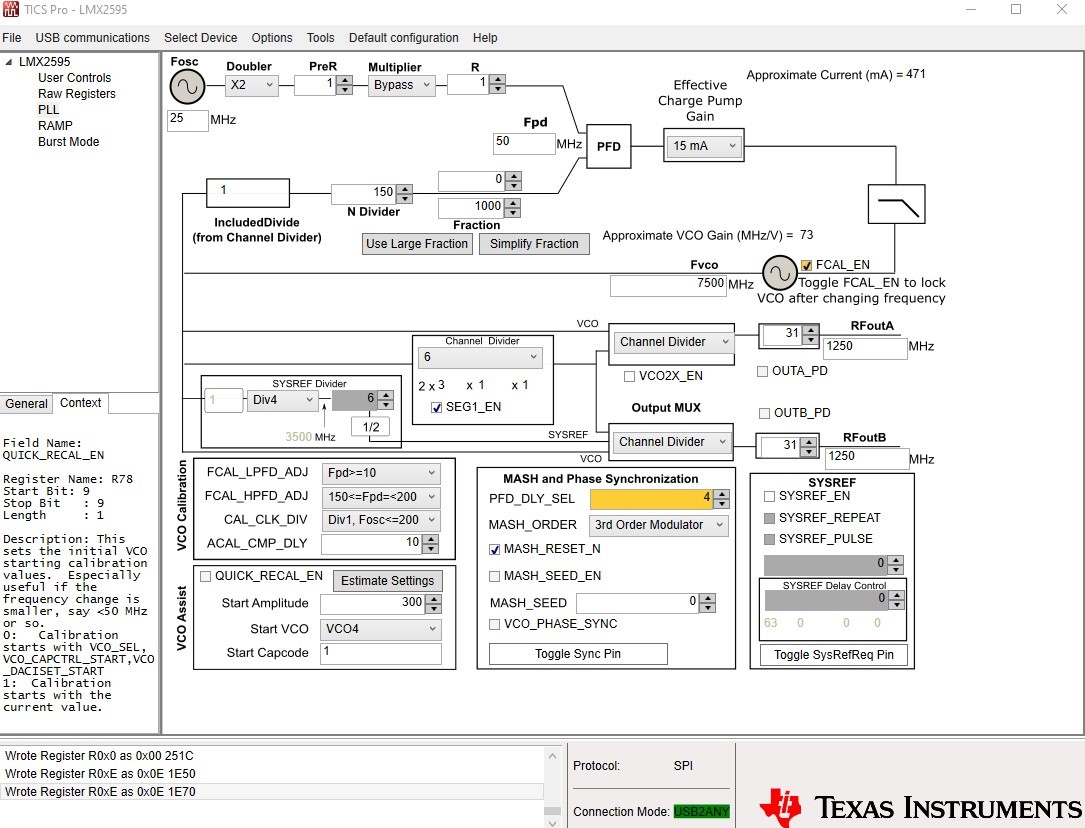

The input signal is generated using a LMX2595 evaluation board.

I'm using the same 25MHz reference clock for both boards.

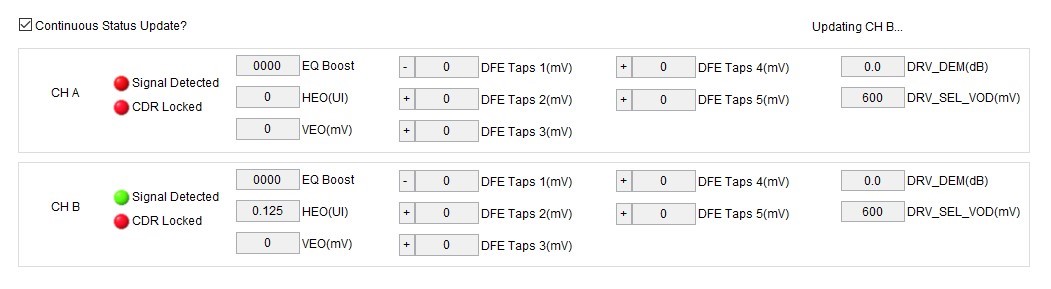

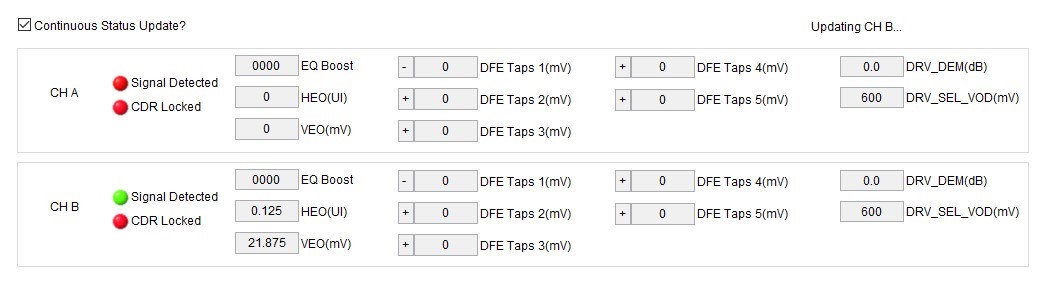

Unfortunately, the CDR of the DS110DF111 device can't achieve to be locked, even if I manually specify the frequency of the input signal.

Do you have any information that should solve my problem ?

Per advance thank you

Mickael