Hi team,

this is brandon, customer and i met some question while using ds110df111:

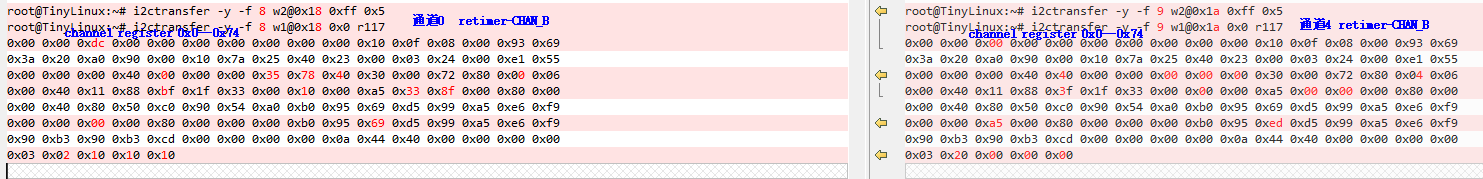

- one of the input source is intel xl710 NIC with10G SFI.0x51 signal dectect is 0, output to XFI. anonther channel input source is 10G XFI, signal dectect is 1, output to the SFI on xl710 NIC. currently,the two channel both link-down. what could be the root cause of this issues and any special configuration should be set?

- DS110DF111 is configured to loop by seting CHAN_REG to 0x54. is the IN signal sent back as the orginal one? or after the internal cdr processing on retimer? does the retimer configuration have any effect on its loopback function

BR

Brandon