Other Parts Discussed in Thread: TCA9617A

Hello,

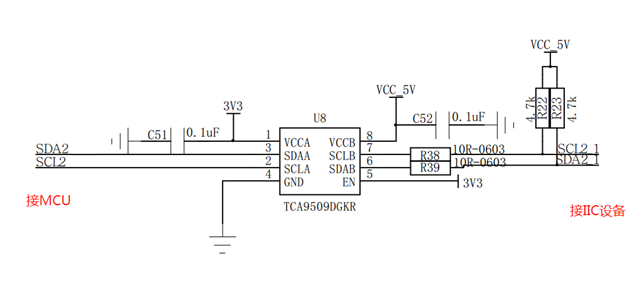

when we use TI's IIC level conversion chip, we have the following exceptions:

Question:

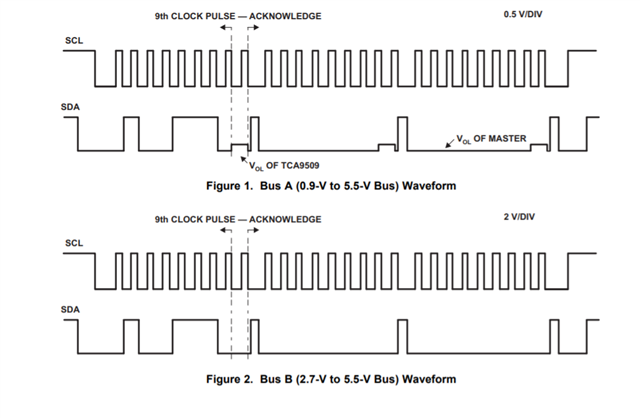

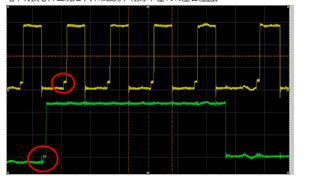

When TCA9509 is connected, the output waveform of the clock and data output of the master control is abnormal (as follows, yellow is the clock and blue is the data), but the conversion output level of TCA9509 is normal

The red circle is the abnormal part, which is stuck at about 10% and has lasted for 300nS.

Results of experiments done:

Remove the chip TCA9509 test controller output waveform: OK

Convert chip TCA9509 other side waveform: OK

Replace and remove pull-up resistors or resistance values on left and right sides: no improvement.

Please provide technical support, thank you.