Dear Team,

Our Customer have a issue as below:

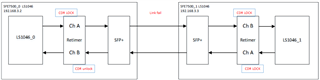

If the CDR Lock is successfully locked, the 16th pin LOCK signal should be high.

If the Lock signal is low, it should mean that CDR Lock failed.

Could you guide us if 16th pin LOCK signal is low, how to resolve CDR Lock failed issue?

Many Thanks,

Denny