Other Parts Discussed in Thread: LSF0204, TXS0102

Hi team,

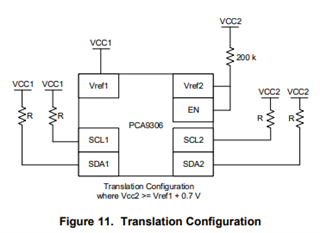

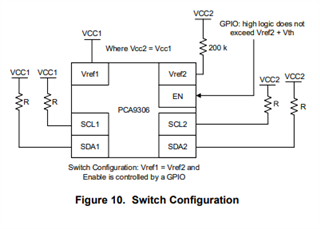

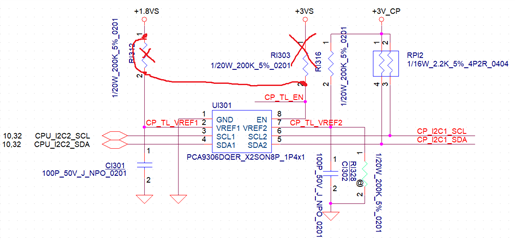

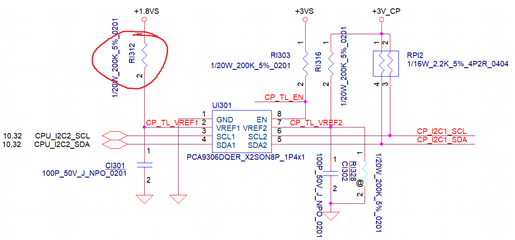

For PCA9306, customer proposed below schematic. Would you please help to review please?

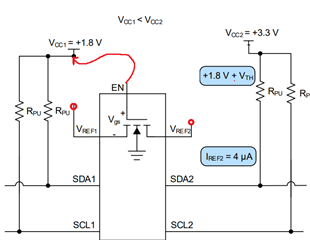

Key concern for customer is +3V_CP comes earlier than +1.8Vs, and +3VS (the EN pin) comes latest. Will there be leakage concern based on this design?

My idea on the schematic is the RI312 200K pull high to 1.8V should be removed, is that understanding correct?

Thanks

Max