Hello.

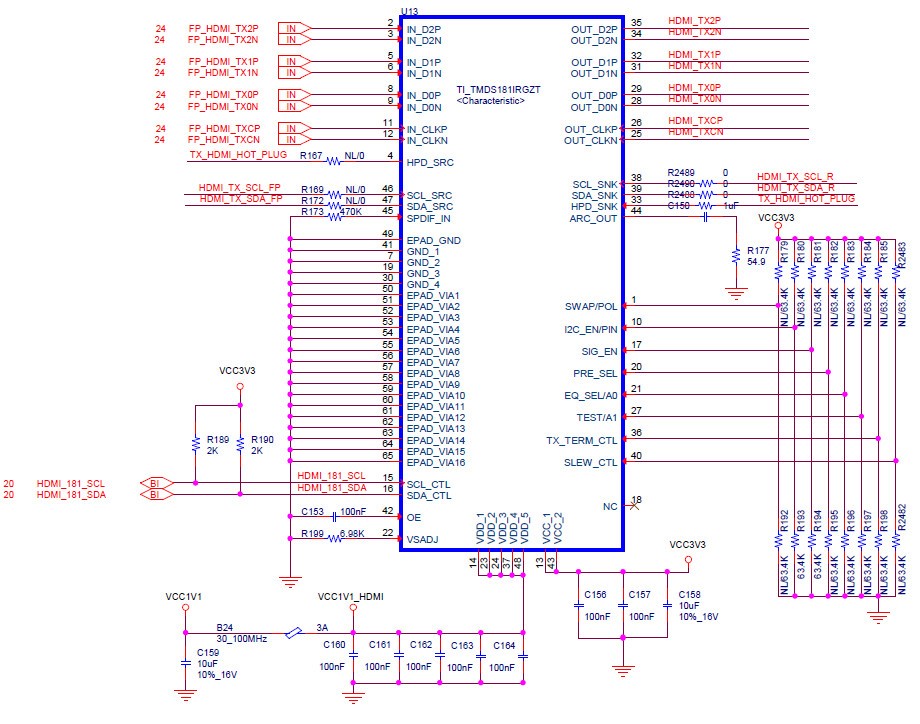

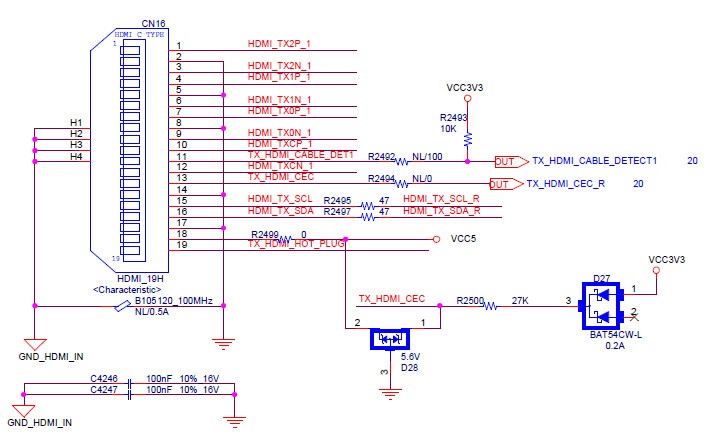

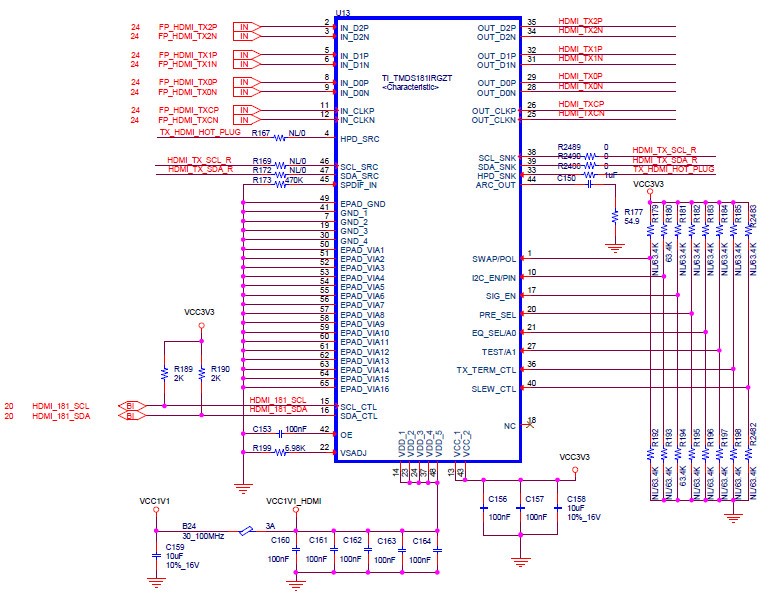

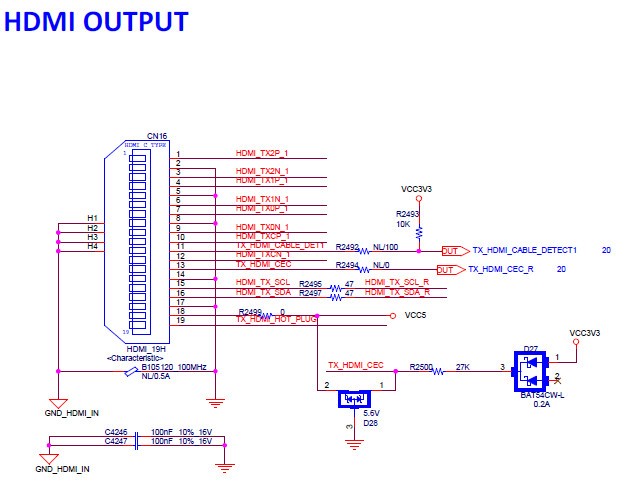

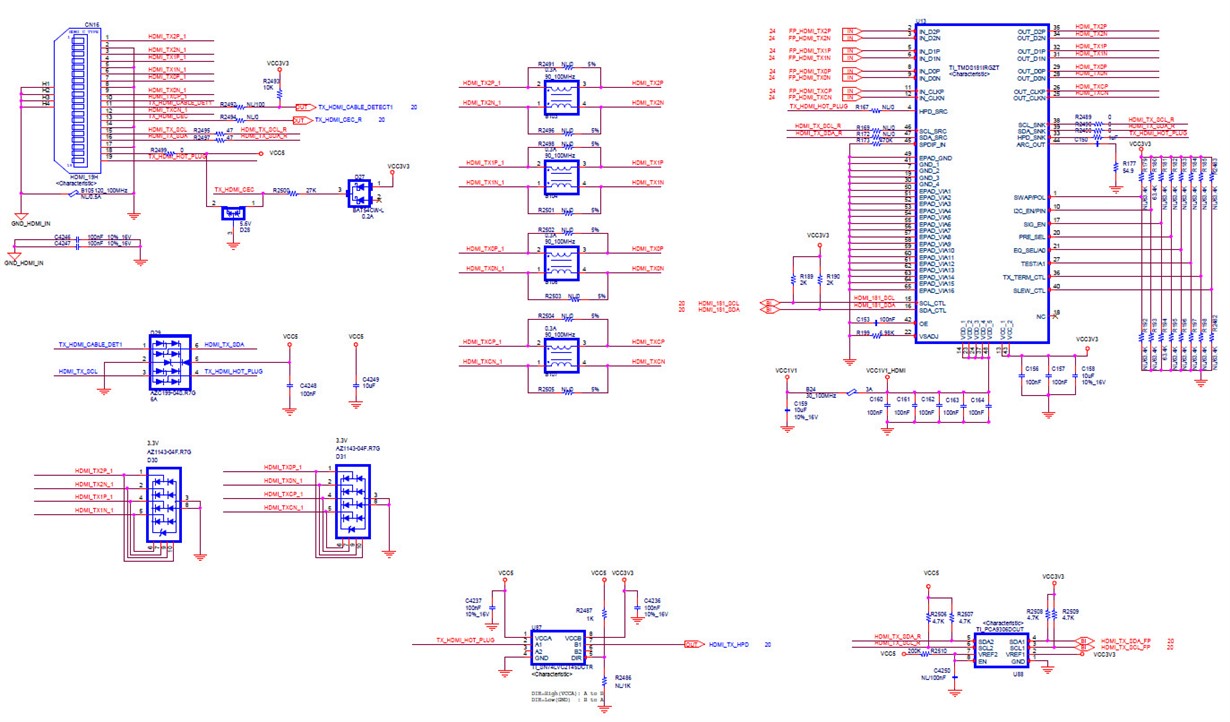

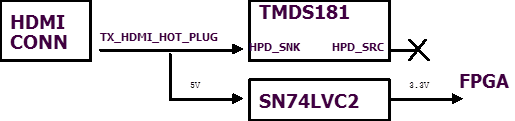

We have a project used TMDS181 on source side. We Read 0x20 Bit[7] always is 1 (Power Down) and check OE pin status is high.

Below is schematic and Register for you reference. Please kindly help comment which Register need be changed. Thanks~

[Mon Jan 22 18:37:01.010 2018] (32) ADDR: 0 DATA: 54

[Mon Jan 22 18:37:01.032 2018] (32) ADDR: 1 DATA: 4D

[Mon Jan 22 18:37:01.056 2018] (32) ADDR: 2 DATA: 44

[Mon Jan 22 18:37:01.081 2018] (32) ADDR: 3 DATA: 53

[Mon Jan 22 18:37:01.104 2018] (32) ADDR: 4 DATA: 31

[Mon Jan 22 18:37:01.128 2018] (32) ADDR: 5 DATA: 38

[Mon Jan 22 18:37:01.155 2018] (32) ADDR: 6 DATA: 31

[Mon Jan 22 18:37:01.177 2018] (32) ADDR: 7 DATA: 20

[Mon Jan 22 18:37:01.201 2018] (32) ADDR: 8 DATA: 1

[Mon Jan 22 18:37:01.222 2018] (32) ADDR: 9 DATA: 2

[Mon Jan 22 18:37:01.245 2018] (32) ADDR: A DATA: 31

[Mon Jan 22 18:37:01.269 2018] (32) ADDR: B DATA: 0

[Mon Jan 22 18:37:01.291 2018] (32) ADDR: C DATA: 0

[Mon Jan 22 18:37:01.315 2018] (32) ADDR: D DATA: 3E

[Mon Jan 22 18:37:01.338 2018] (32) ADDR: E DATA: 0

[Mon Jan 22 18:37:01.361 2018] (32) ADDR: F DATA: F

[Mon Jan 22 18:37:01.387 2018] (32) ADDR: 10 DATA: 0

[Mon Jan 22 18:37:01.408 2018] (32) ADDR: 11 DATA: 0

[Mon Jan 22 18:37:01.432 2018] (32) ADDR: 12 DATA: 0

[Mon Jan 22 18:37:01.456 2018] (32) ADDR: 13 DATA: 0

[Mon Jan 22 18:37:01.480 2018] (32) ADDR: 14 DATA: 0

[Mon Jan 22 18:37:01.504 2018] (32) ADDR: 15 DATA: 80

[Mon Jan 22 18:37:01.529 2018] (32) ADDR: 16 DATA: 0

[Mon Jan 22 18:37:01.555 2018] (32) ADDR: 17 DATA: 0

[Mon Jan 22 18:37:01.577 2018] (32) ADDR: 18 DATA: 0

[Mon Jan 22 18:37:01.601 2018] (32) ADDR: 19 DATA: 0

[Mon Jan 22 18:37:01.625 2018] (32) ADDR: 1A DATA: 0

[Mon Jan 22 18:37:01.649 2018] (32) ADDR: 1B DATA: 0

[Mon Jan 22 18:37:01.672 2018] (32) ADDR: 1C DATA: 0

[Mon Jan 22 18:37:01.697 2018] (32) ADDR: 1D DATA: 0

[Mon Jan 22 18:37:01.720 2018] (32) ADDR: 1E DATA: 10

[Mon Jan 22 18:37:01.746 2018] (32) ADDR: 1F DATA: 4

[Mon Jan 22 18:37:01.769 2018] (32) ADDR: 20 DATA: E8