Hi,

My project uses a DP159 as DisplayPort Retimer, the FPGA is xilinx XC7Z015. I am using DisplayPort RX Subsystem v2.1 in the design ,the driver is provided by xilinx SDK, however the link training was always failed, no reference clock output from out_clkp/out_clkn.

The GPU is nVidia GTX1080, when the program runs, dp159 get hot.... The dp159 package marking is TI 77I AOGO G4.

(a)Does it related to dp159 silicon revision?

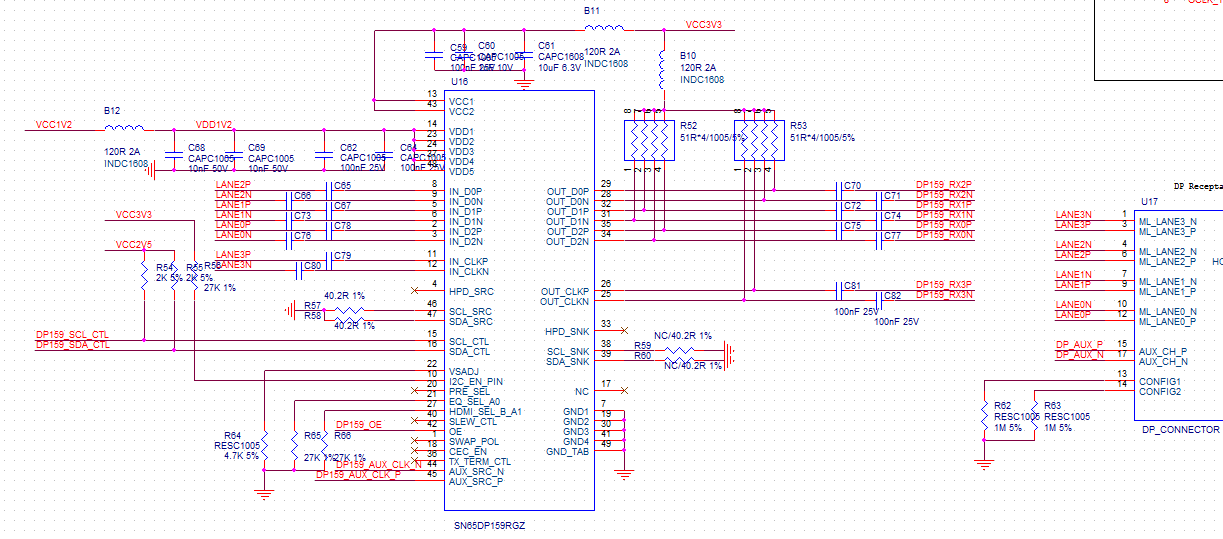

(b) as slla358 says, there are two possible implementations for HPD: HPD routed around DP159 or HDP routed thru DP159, my board chooses route around HPD.

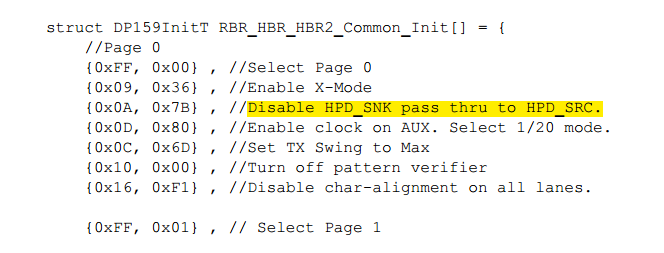

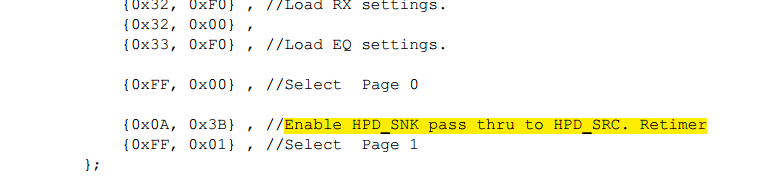

but software Initial process first disabled HPD pass through and then enable HPD through DP159. Is it OK to commend {0x0A, 0x3B} ?

(b) /* DP159 Initialize */

{0xFF, 0x00},

{0x09, 0x36},

{0x0A, 0x7B},

{0x0D, 0x80},

{0x0C, 0x6D},

{0x10, 0x00},

{0x16, 0xF1},

{0xFF, 0x01},

{0x00, 0x02},

{0x04, 0x80},

{0x05, 0x00},

{0x08, 0x00},

{0x0D, 0x02},

{0x0E, 0x03},

{0x01, 0x01},

{0x02, 0x3F},

{0x0B, 0x33},

{0xA1, 0x02},

{0xA4, 0x02},

{0x10, 0xF0},

{0x11, 0x30},

{0x14, 0x00},

{0x12, 0x03},

{0x13, 0xFF},

{0x13, 0x00},

{0x30, 0xE0},

{0x32, 0x00},

{0x31, 0x00},

{0x4D, 0x08},

{0x4C, 0x01},

{0x34, 0x01},

{0x32, 0xF0},

{0x32, 0x00},

{0x33, 0xF0},

{0xFF, 0x00},

{0x0A, 0x3B},

{0xFF, 0x01}

(c ) /* link training */

switch (ConfigType) {

case XDPRXSS_DP159_CT_TP1:

/* Enable bandgap, DISABLE PLL, clear A_LOCK_OVR */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x00, 0x02);

/* CP_EN = PLL (reference) mode */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x01, 0x01);

/* Set PLL control */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x0B, 0x33);

/* Set CP_CURRENT */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x02, 0x3F);

LCount = (LaneCount == XDPRXSS_DP159_LANE_COUNT_1) ?

0xE1 : (LaneCount == XDPRXSS_DP159_LANE_COUNT_2) ?

0xC3:0x0F;

LRate = (LinkRate == XDPRXSS_DP159_HBR2)? 0x0:

(LinkRate == XDPRXSS_DP159_HBR) ? 0x1 : 0x2;

/* Enable RX lanes */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x30, LCount);

/* Enable Bandgap, Enable PLL, clear A_LOCK_OVR */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x00, 0x03);

/* Enable fixed EQ (to reset adaptive EQ logic) */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x4C, 0x01);

/* Set EQFTC and EQLEV (fixed EQ) */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x4D, (LRate << 4) |

(XDPRXSS_DP159_EQ_LEV & 0x0F));

if (LinkRate == XDPRXSS_DP159_HBR2) {

Cpi = XDPRXSS_DP159_CPI_PD_HBR2;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_HBR2;

}

else if (LinkRate == XDPRXSS_DP159_HBR) {

Cpi = XDPRXSS_DP159_CPI_PD_HBR;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_HBR;

}

else {

Cpi = XDPRXSS_DP159_CPI_PD_RBR;

PllCtrl = XDPRXSS_DP159_PLL_CTRL_PD_RBR;

}

/* Enable TX lanes */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x10, LCount);

/* Enable PLL and Bandgap, set A_LOCK_OVR, and set

* expand LPRES

*/

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x00, 0x23);

/* Wait for PLL lock */

while ((ReadBuf == 0) && (Counter <

XDPRXSS_DP159_LOCK_WAIT)) {

XDpRxSs_Dp159Read(InstancePtr,

XDPRXSS_DP159_IIC_SLAVE, 0x00, &ReadBuf);

ReadBuf &= 0x40; /* Lock status. */

Counter++;

}

/* CP_CURRENT */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x02, Cpi);

/* Set PLL Control */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x0B, PllCtrl);

/* CP_EN is PD mode */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x01, 0x02);

/* Select page 0*/

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0xFF, 0x00);

/* Set DP_TST_EN per #lanes, latch FIFO errors */

LCount = (LaneCount == XDPRXSS_DP159_LANE_COUNT_1) ?

0x11 : (LaneCount ==

XDPRXSS_DP159_LANE_COUNT_2) ?

0x31 : 0xF1;

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x16, LCount);

/* Disable PV, allows char-align and 8b10 decode to

* operate

*/

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x10, 0x00);

/* Select page 1 */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0xFF, 0x01);

break;

case XDPRXSS_DP159_CT_TP2:

case XDPRXSS_DP159_CT_TP3:

/* Enable adaptive EQ */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x4C, 0x03);

/* Select page 0 */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0xFF, 0x00);

/* Clear BERT counters and TST_INTQ latches --

* Self-clearing in DP159

*/

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0x15, 0x18);

/* Select page 1 */

XDpRxSs_Dp159Write(InstancePtr, XDPRXSS_DP159_IIC_SLAVE,

0xFF, 0x01);

break;

}