Tool/software: Linux

Our customer meets an emergency issue and need help!

Their company have a RSB-468 project and product 15pcs, and find 6pcs LAN up/down fail. The specific description is:

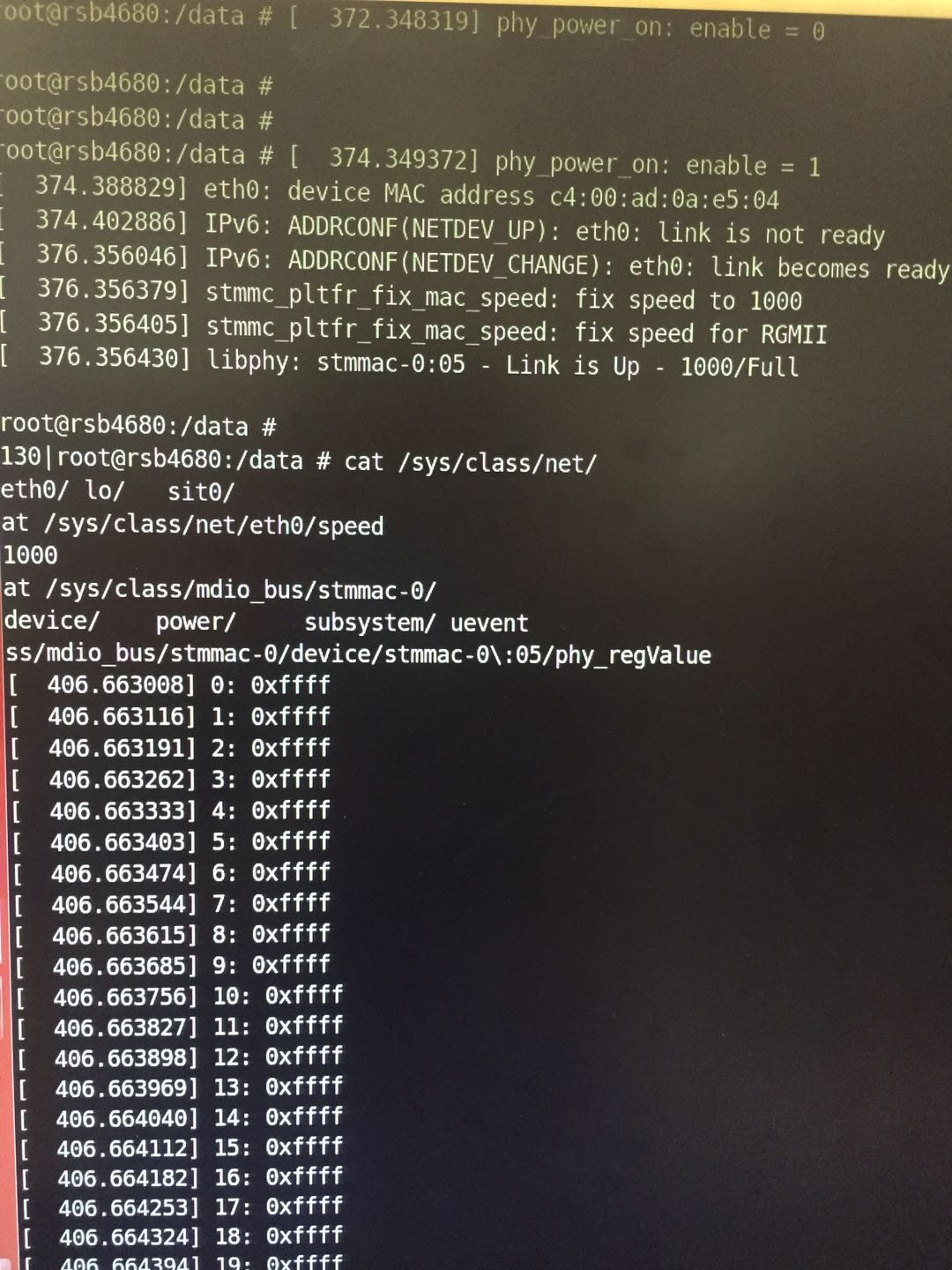

Disable LAN and then Enable LAN,LAN would have no function, must reboot or enable many times then the function is OK.

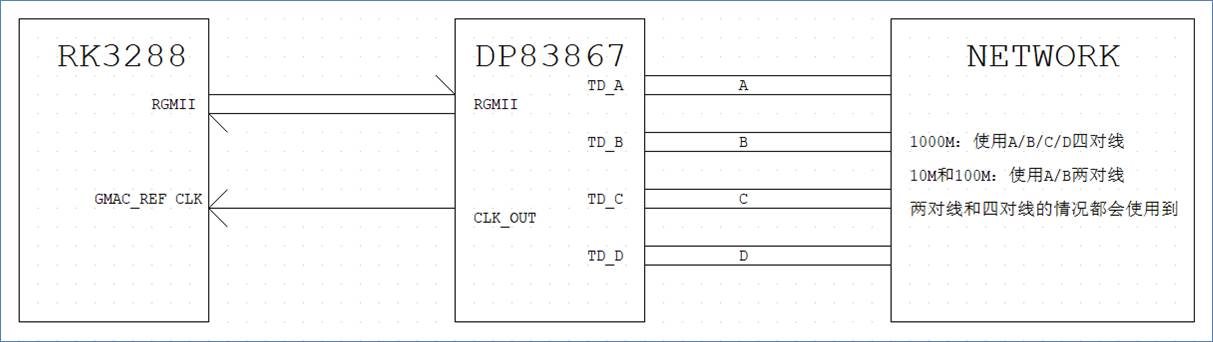

(TI LAN PHY DP83867IRRGZT)

1. User environment: android6.0 (kernel3.10),if config eth0 down/up, then will meets the problem randomly.

2. Their engineer configed register like this:

//address mask value

0x0014 0x200 0x200

0x0018 0xfff 0x65b

0x001e 0x200 0x200

0x0032 0x3 0x3

0x0086 0xff 0x80

0x0170 0x1f00 0x0000