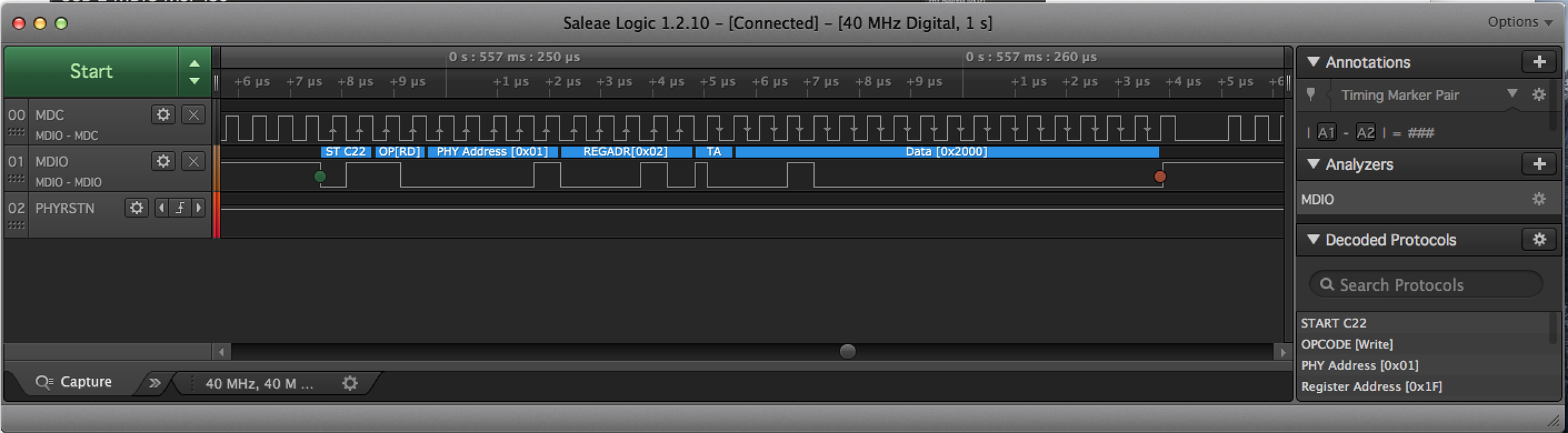

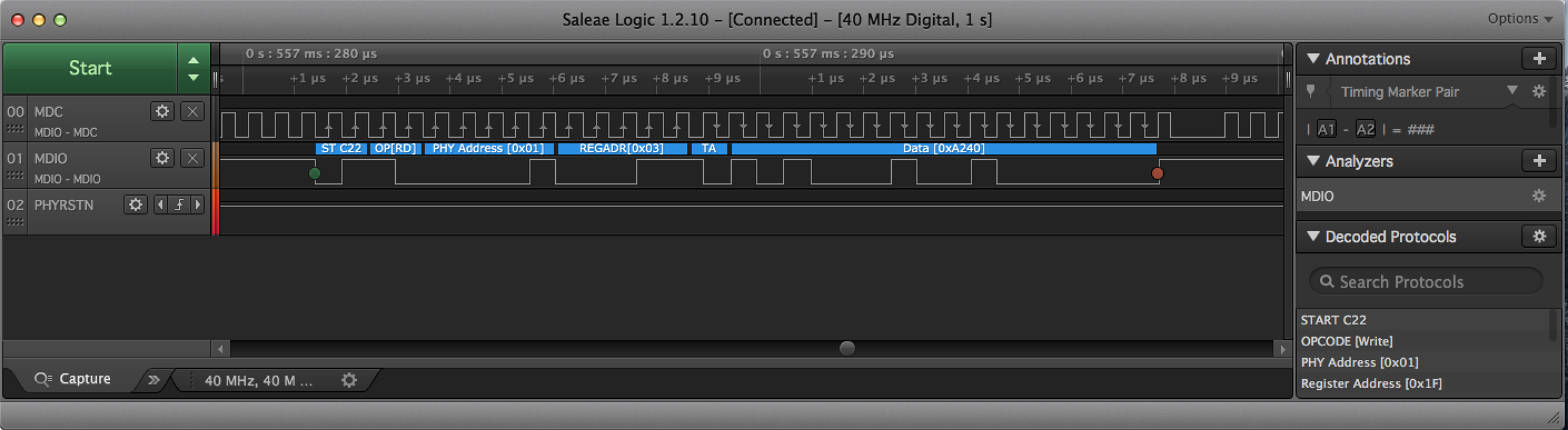

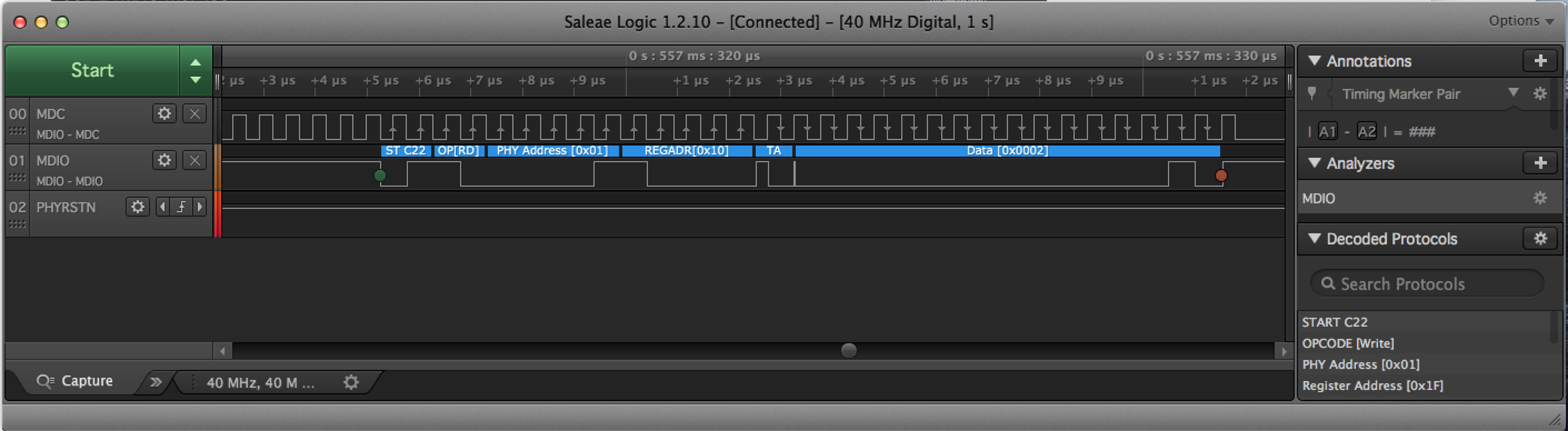

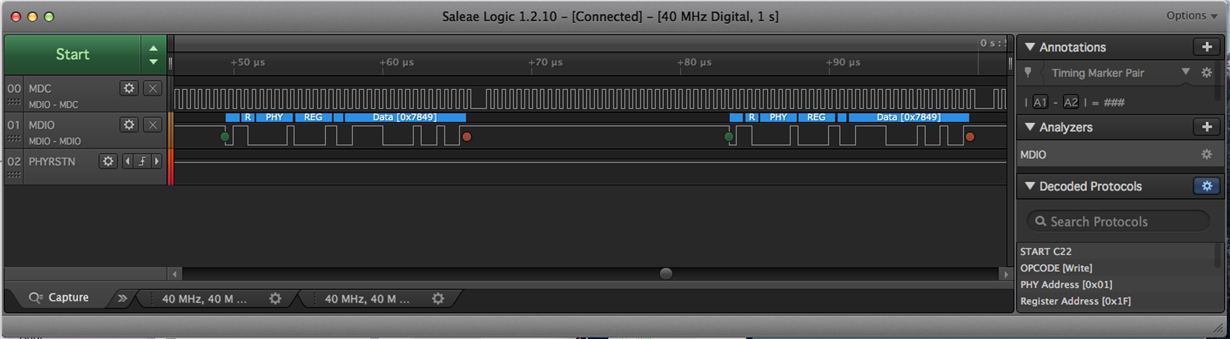

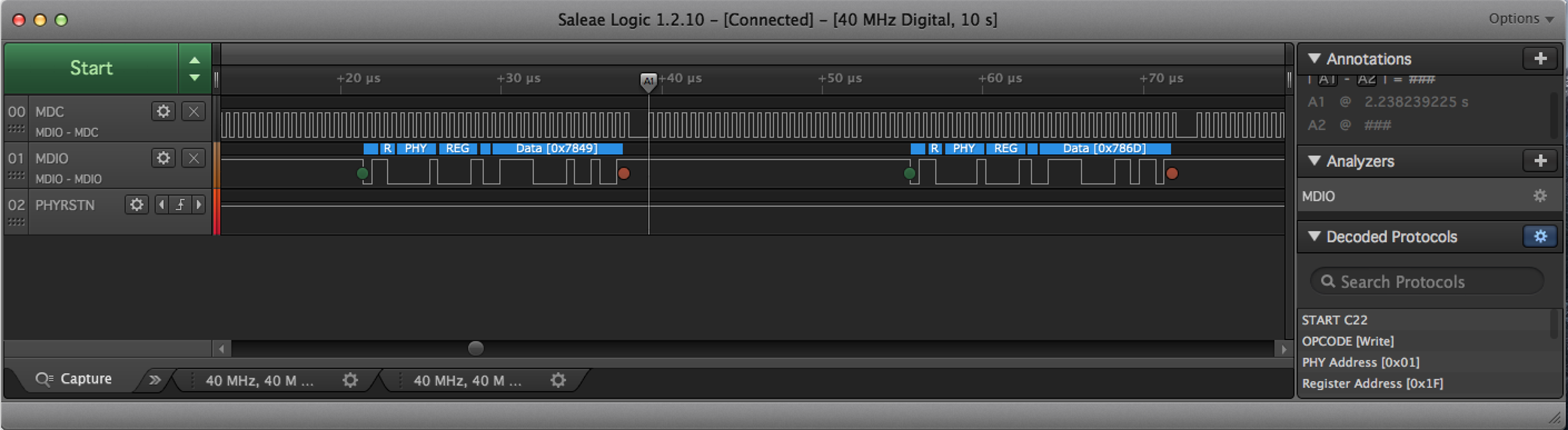

When trying to read register 0x0001 Basic Mode Status Register through MDIO the result is 0x7849 which denotes that the link and auto-negotiation bits are off. The LEDs show that the link and auto-negotiation have been completed. If in the software the values read are override by the expected value 0x786D then the expected result is observed which is a working http server, and thus the ethernet phy working correctly.

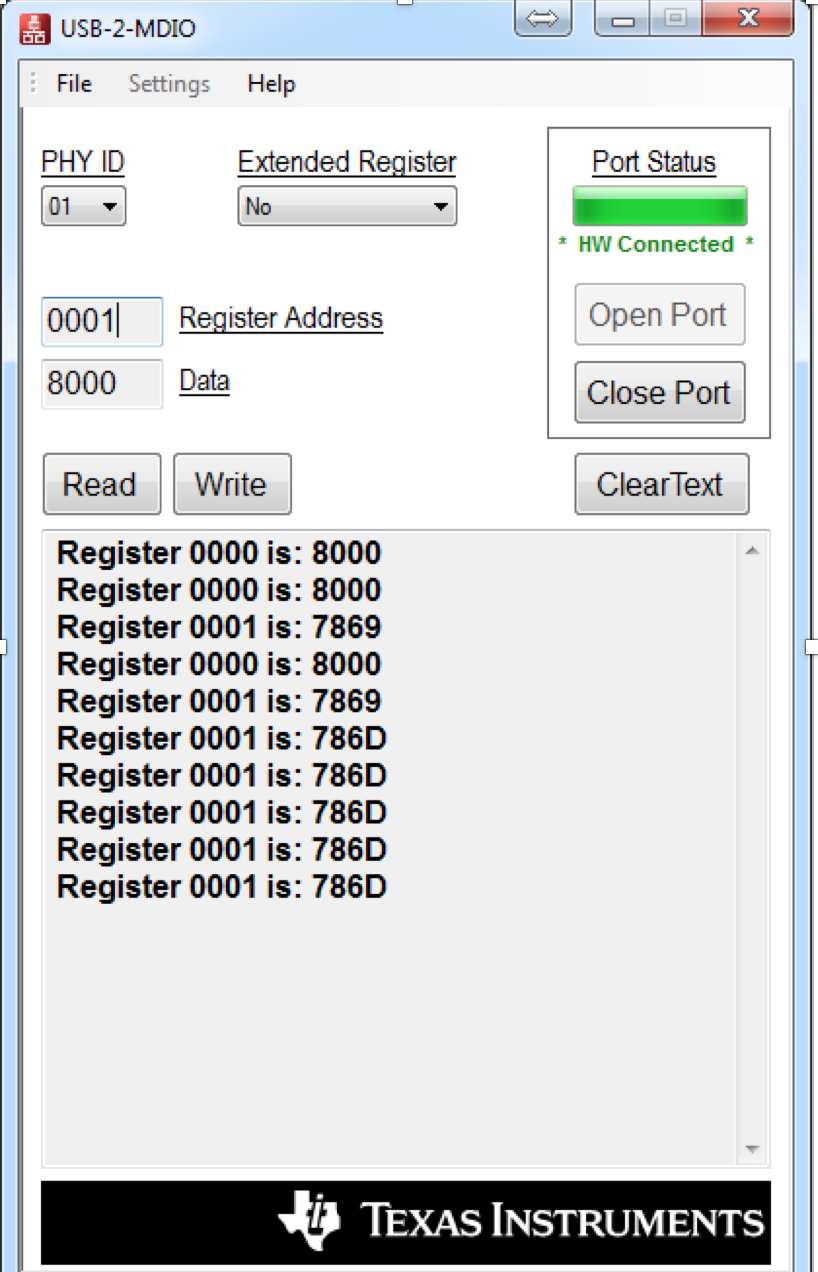

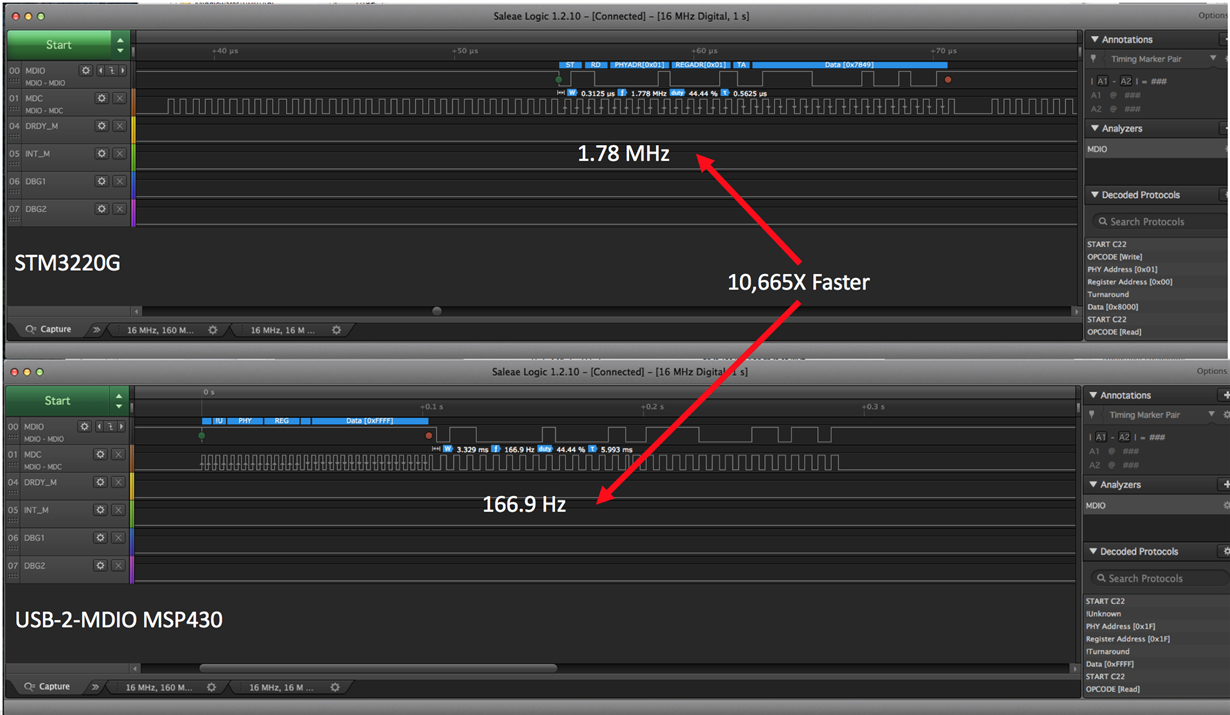

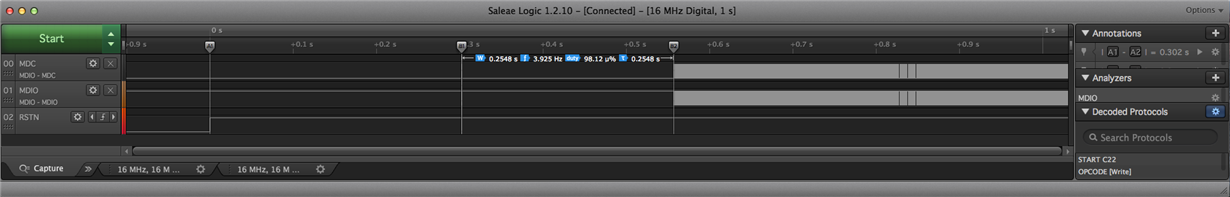

By using the launchpad and the USB-2-MDIO software and a MSP-430 launchpad, I am able to read the correct values. The difference is that the launchpad reads at a speed of 200 Hz while the board we are using reads at 2 MHz. The problem was thought to be due to wiring the MAC to the PHY externally. To our surprise, the same issue appeared on the design on the PCB.

By using a different external board with the same processor but on a different running MDIO at 2 MHz, the correct values are read.

Is this an intermittent failure due to some timing issues? Does not make sense to have the external signal indicate link and auto-negotiation and not reflected on the register corresponding bits.