[ MAX3232E-Q1 ] Waveforms

Hi,

My customer has been evaluating MAX3232E-Q1 on their board.

Can you help to review their waveforms as below?

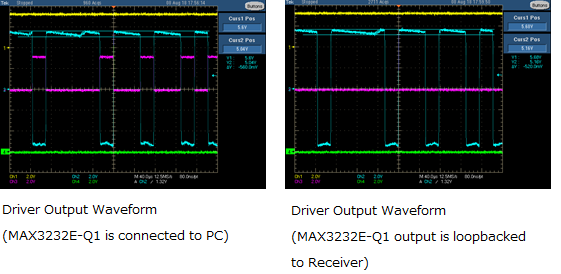

<Q1: Voltage Bump on each High and Low>:

As you can see, the high and low level are dropped a bit while maintaining its level.

If it's measure without any load condition (open), no voltage drop can be seen.

Is this expected?

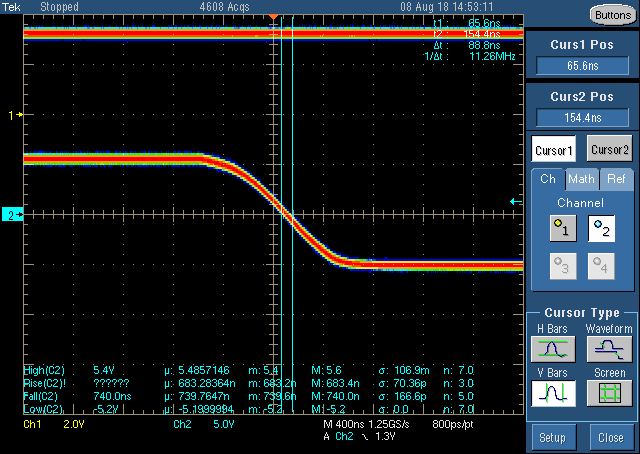

<Q2: Jitter>:

The jitter is somewhere around 90nS.

Is this what we expect?

Are there any jitter requirements on the industrial standard?

Thanks,

Ken