Other Parts Discussed in Thread: DSI-TUNER, SN65DSI83

Hi,

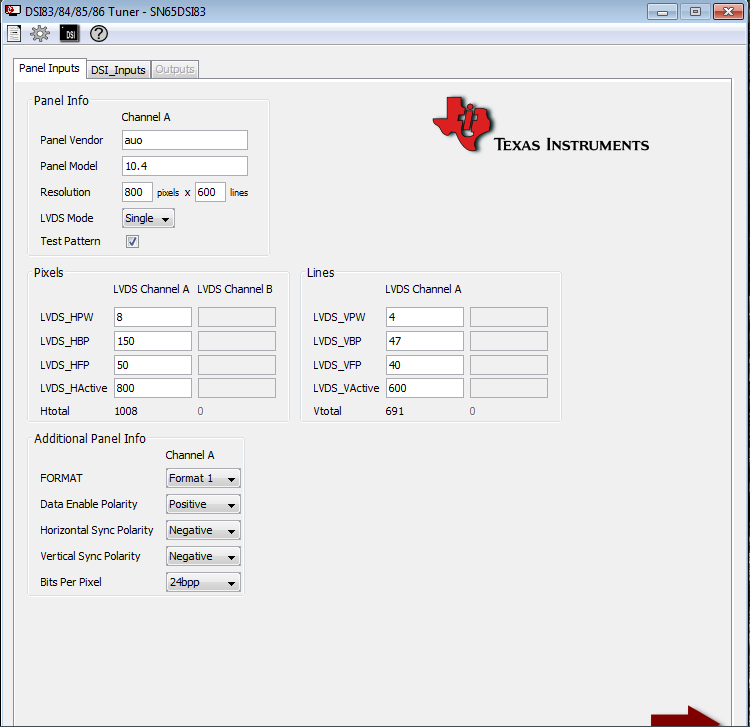

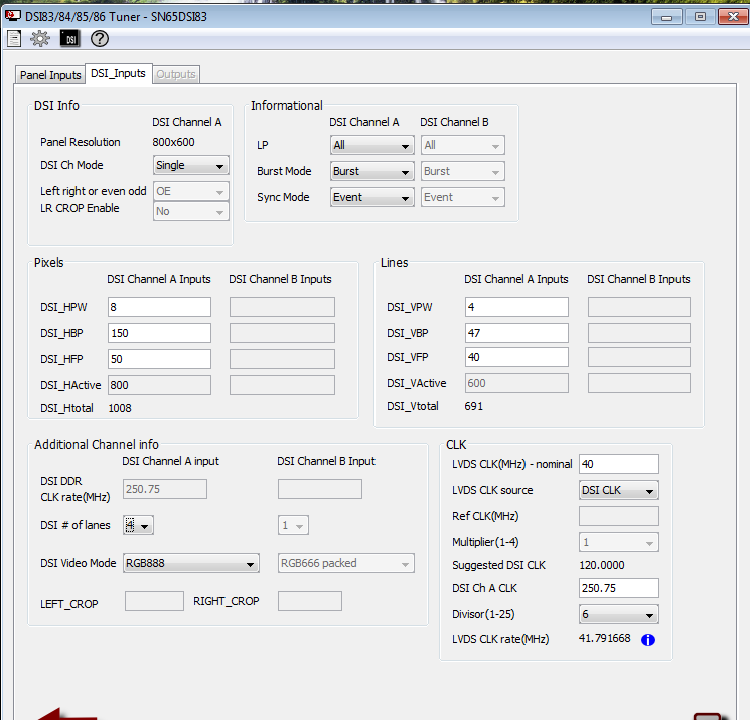

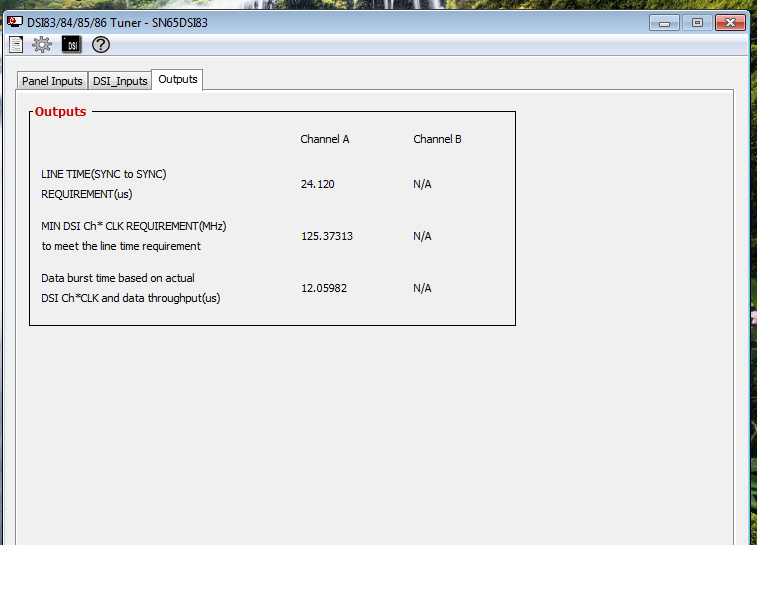

we are using SN65DSI83-Q1, i have interfaced with LVDS panel configured through the I2C, following value are write in registers

i2cWriteByte(i2c_fd,0x09,0x00); //software reset

usleep(10000);

i2cWriteByte(i2c_fd,0x0D,0x00); //PLL register disable mode

usleep(10000);

i2cWriteByte(i2c_fd,0x0A,0x03); //set lvds clock range //don't change this

usleep(10000);

i2cWriteByte(i2c_fd,0x0B,0x40); //dsi clock divider //

usleep(10000);

i2cWriteByte(i2c_fd,0x10,0x00); //Lane configuration

usleep(10000);

i2cWriteByte(i2c_fd,0x11,0x00); //equalization

usleep(10000);

i2cWriteByte(i2c_fd,0x12,0x30); //DSI clock range

usleep(10000);

i2cWriteByte(i2c_fd,0x18,0xE8);//7A //data bit format

usleep(10000);

i2cWriteByte(i2c_fd,0x19,0x02); //control the differential voltage

usleep(10000);

i2cWriteByte(i2c_fd,0x1A,0x02); //lvds differential termination

usleep(10000);

i2cWriteByte(i2c_fd,0x1B,0x10); //commmon mode voltage

usleep(10000);

i2cWriteByte(i2c_fd,0x20,0x20); //horizontal length low

usleep(10000);

i2cWriteByte(i2c_fd,0x21,0x03); //horizontal length High

usleep(10000);

i2cWriteByte(i2c_fd,0x24,0x58); //vertical display low3

usleep(10000);

i2cWriteByte(i2c_fd,0x25,0x02); //vertical display High

usleep(10000);

i2cWriteByte(i2c_fd,0x28,0x9c); //sync delay low

usleep(10000);

i2cWriteByte(i2c_fd,0x29,0x07); //sync delay High

usleep(10000);

i2cWriteByte(i2c_fd,0x2C,0x08); //Hsync Pulse width low

i2cWriteByte(i2c_fd,0x2D,0x00); //Hsync Pulse width High

i2cWriteByte(i2c_fd,0x30,0x04); //Vsync Pulse width low

i2cWriteByte(i2c_fd,0x31,0x00); //Vsync Pulse width High

i2cWriteByte(i2c_fd,0x34,0x96); //HORIZONTAL_BACK_PORCH

i2cWriteByte(i2c_fd,0x36,0x2F); //VERTICAL_BACK_PORCH

i2cWriteByte(i2c_fd,0x38,0x32); //HORIZONTAL_FRONT_PORCH

i2cWriteByte(i2c_fd,0x3A,0x28); //HORIZONTAL_FRONT_PORCH

i2cWriteByte(i2c_fd,0x3C,0x10); //Test Pattern Enable

usleep(10000); //10 ms delay

i2cWriteByte(i2c_fd,0x0D,0x01); // enable the PLL

usleep(10000); //10 ms delay

i2cWriteByte(i2c_fd,0x09,0x01); // software reset

usleep(10000); //10 ms delay

printf("writing completed....\n");

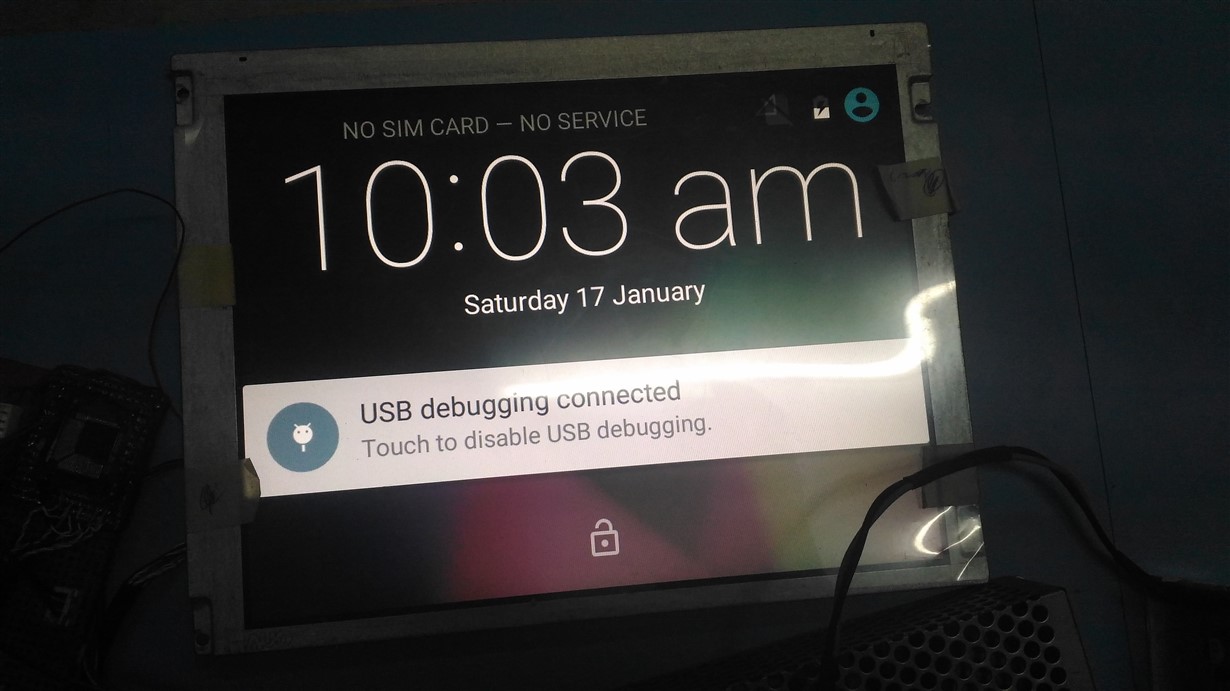

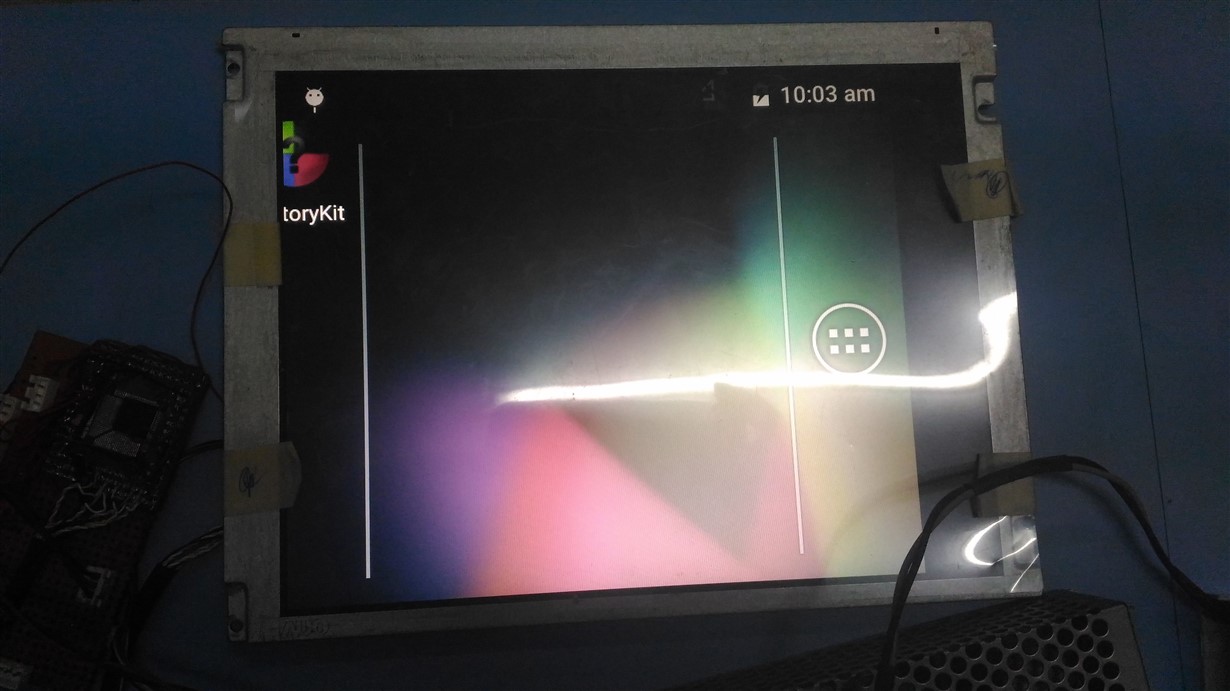

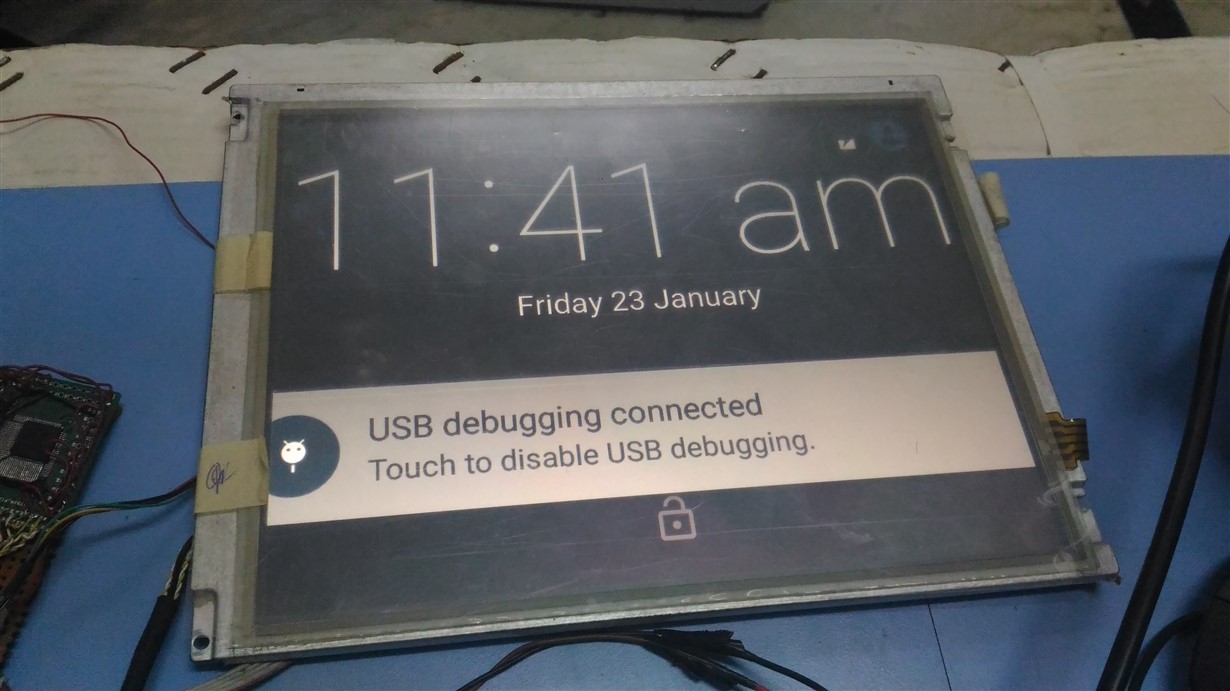

After write these values panel did not show the test pattern. i didn't give any DSI signal and clock to the SN65DSI83-Q1. If i made any mistake please correct me, my panel data sheet attached here.

Thank you....up-02-123.pdf