Other Parts Discussed in Thread: TIDA-00421, ALP

Hi,

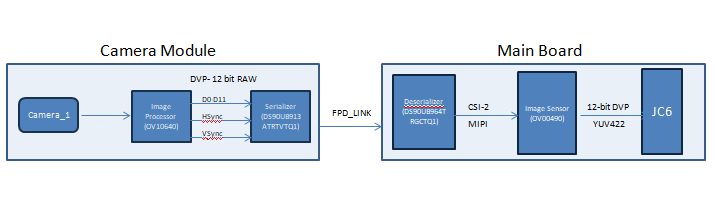

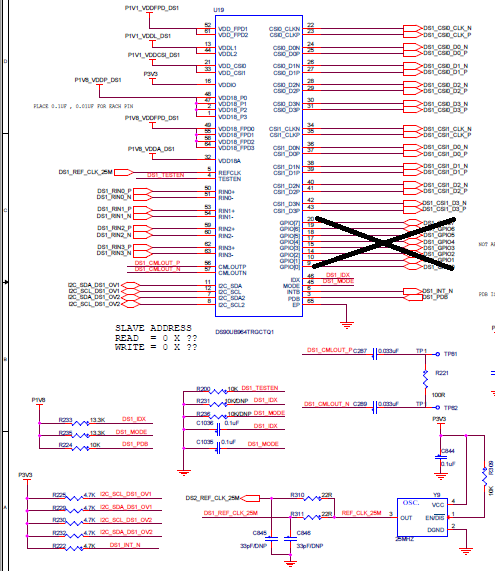

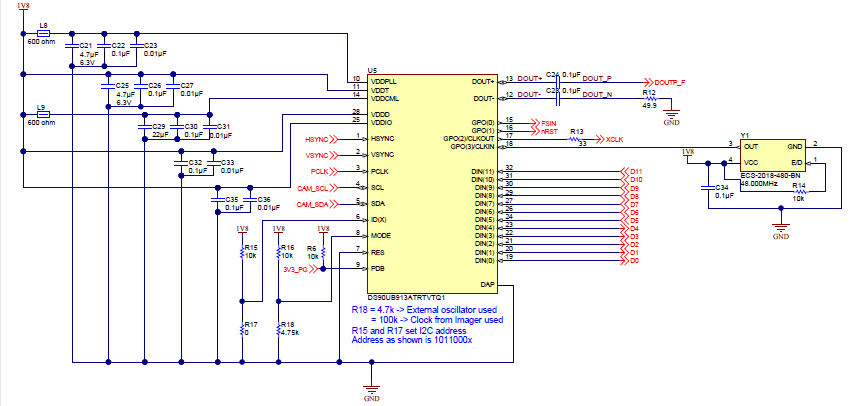

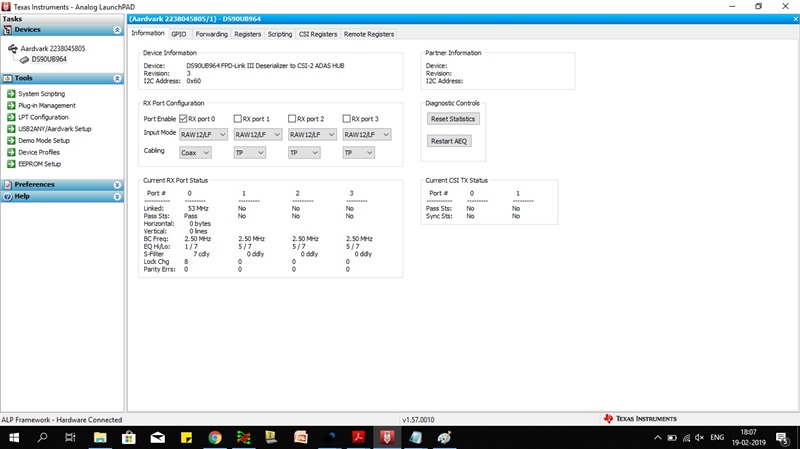

We have built camera module using TIDA-00421 gerber from TI. We are using DS90UB964 deserialiser on our main board. Serialiser and deserialisers are connected using FPD link-III.

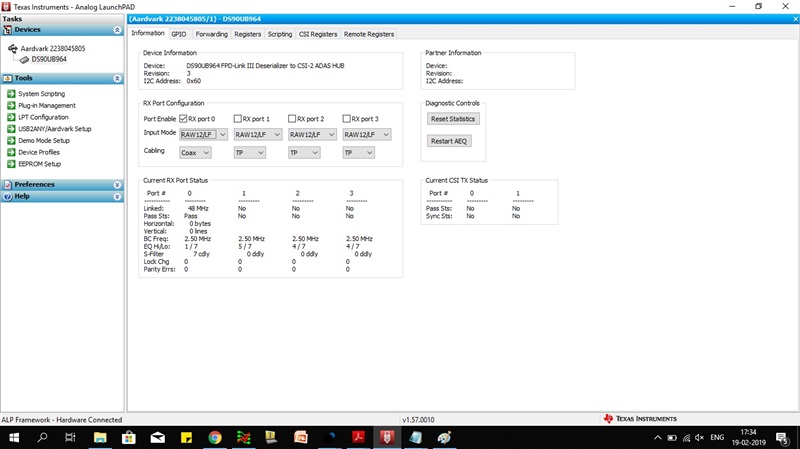

After image sensor and SerDes configuration we are able to see data at image sensor output (Oscilloscope probe). But we do not see data at serialiser and deserialiser output.

Since we are able to see output from image sensor we assume we are missing something in SerDes configuration.

Below are the SerDes commands used as per our requirement. Could you check and suggest if we are missing out any configuration.?

Note: Deserialiser ID(DS90UB964)- 0x30

Serialiser ID (DS90UB913)- 0x5d

.........................................................................

sleep 2;

i2cset -f -y 0 0x30 0x01 0x02;

sleep 2;

i2cset -f -y 0 0x30 0x0c 0xcf;

sleep 2;

i2cset -f -y 0 0x30 0x1f 0x00;

sleep 2;

i2cset -f -y 0 0x30 0x10 0x91;

sleep 2;

i2cset -f -y 0 0x30 0x11 0x85;

sleep 2;

i2cset -f -y 0 0x30 0x13 0x89;

sleep 2;

i2cset -f -y 0 0x30 0x14 0x8d;

sleep 2;

i2cset -f -y 0 0x30 0x19 0x00;

sleep 2;

i2cset -f -y 0 0x30 0x1a 0x8B;

sleep 2;

i2cset -f -y 0 0x30 0x1b 0x04;

sleep 2;

i2cset -f -y 0 0x30 0x1c 0xE2;

echo "half way through"

sleep 2;

i2cset -f -y 0 0x30 0x18 0x01;

sleep 2;

i2cset -f -y 0 0x30 0x4c 0x01;

sleep 2;

i2cset -f -y 0 0x30 0x58 0x58;

sleep 2;

i2cset -f -y 0 0x30 0x5c 0xbb;

sleep 2;

i2cset -f -y 0 0x30 0x5d 0x60;

sleep 2;

i2cset -f -y 0 0x30 0x6d 0x7e;

sleep 2;

i2cset -f -y 0 0x30 0x65 0x63;

sleep 2;

i2cset -f -y 0 0x30 0x7c 0xe0;

sleep 2;

i2cset -f -y 0 0x30 0x70 0x2b;

sleep 2;

i2cset -f -y 0 0x30 0x71 0x2c;

sleep 2;

i2cset -f -y 0 0x30 0x0a 0x16;

sleep 2;

i2cset -f -y 0 0x30 0x0b 0x16;

sleep 2;

i2cset -f -y 0 0x5d 0x01 0x31;

sleep 2;

i2cset -f -y 0 0x5d 0x03 0xc5;

sleep 2;

i2cset -f -y 0 0x5d 0x0d 0x55;

sleep 2;

i2cset -f -y 0 0x5d 0x11 0x16;

sleep 2;

i2cset -f -y 0 0x5d 0x12 0x16;

sleep 2;

i2cset -f -y 0 0x30 0x4c 0x0f;

sleep 2;

i2cset -f -y 0 0x30 0x0f 0x00;

sleep 2;

i2cset -f -y 0 0x30 0x6e 0x9a;

sleep 2;

i2cset -f -y 0 0x30 0x32 0x12;

echo "almost there"

sleep 2;

i2cset -f -y 0 0x30 0x33 0x03;

sleep 2;

i2cset -f -y 0 0x30 0x20 0xfc;

sleep 2;

i2cset -f -y 0 0x30 0x20 0x0c;

sleep 2;

i2cset -f -y 0 0x30 0x21 0x14;

i2cset -f -y 0 0x5d 0x03 0xc5;

i2cset -f -y 0 0x5d 0x0d 0x55;

i2cset -f -y 0 0x5d 0x11 0x16;

i2cset -f -y 0 0x5d 0x12 0x16;

................................................................................

Regards

Bharati