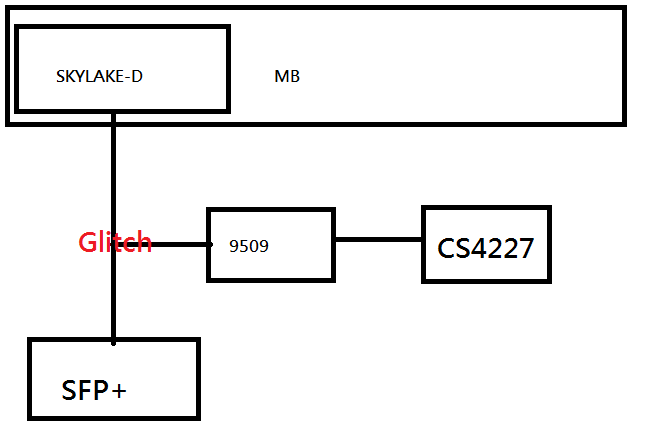

Other Parts Discussed in Thread: TCA9617A, TCA9509

Hello Sirs,

Need your comment .

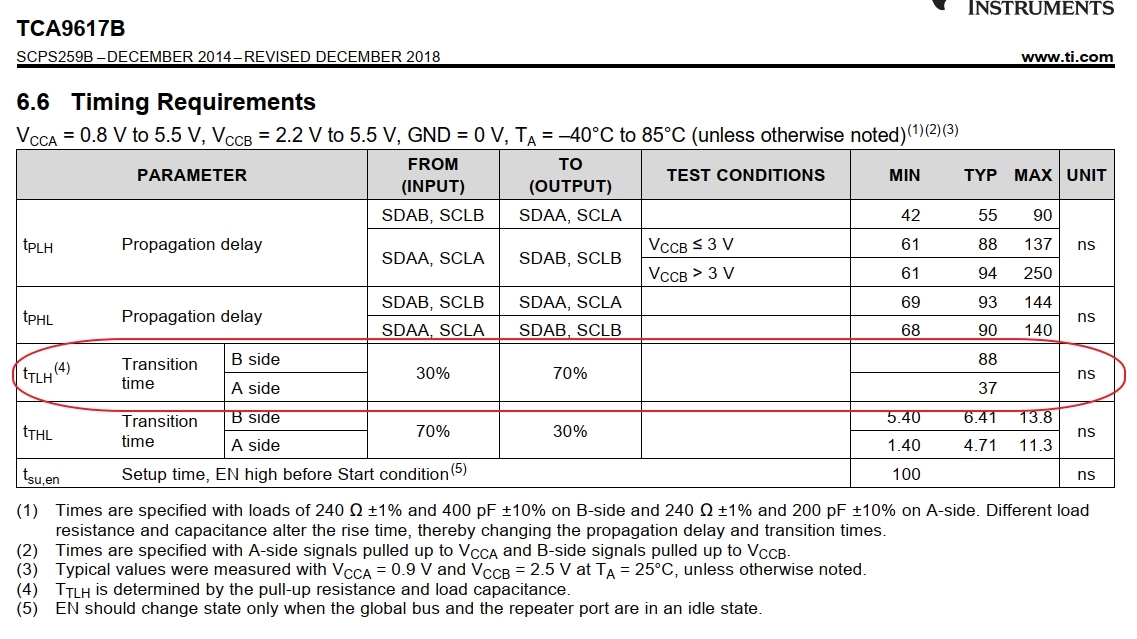

Refer to TCA9617B datasheet 8.3.2 and 6.6 Timing requirements,

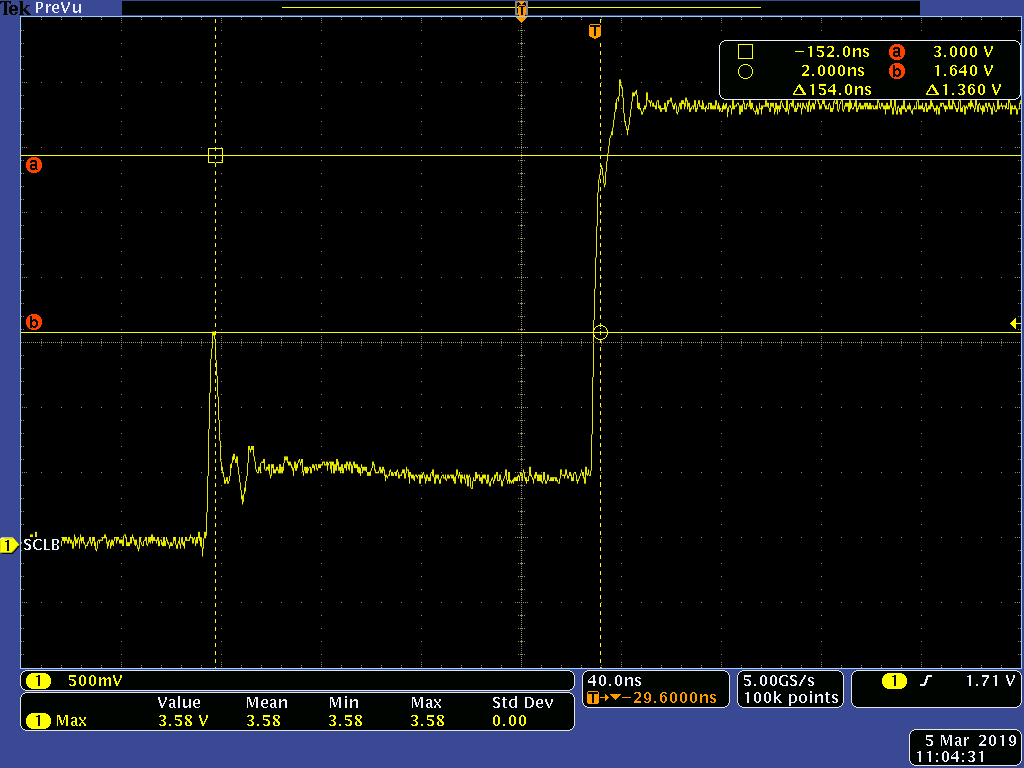

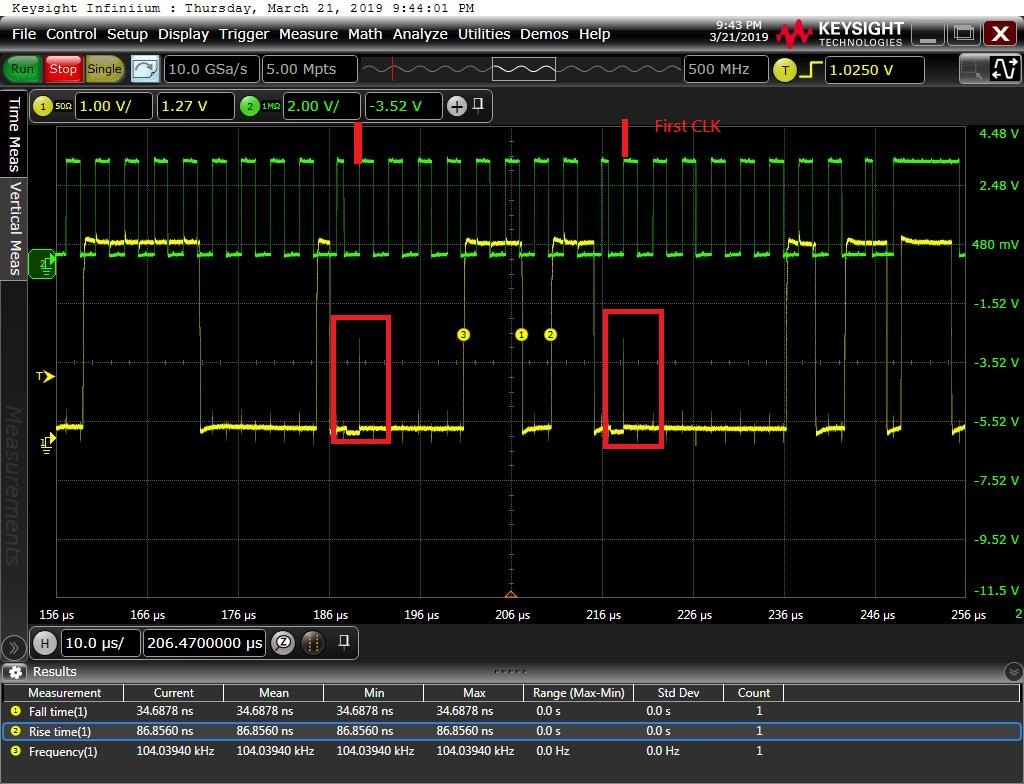

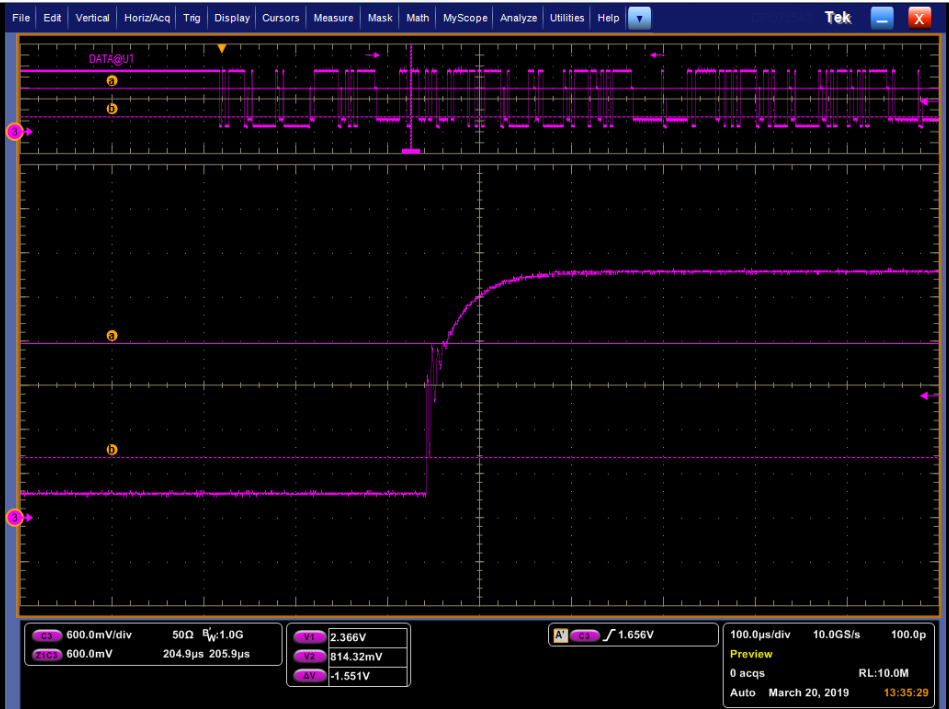

- What's the problem if rising time too fast like attach waveform (B side & 100K pull up resistor) ?

- As waveform , there's a overshoot once the pedestal voltage setup . How to eliminate it ?

Many thanks !

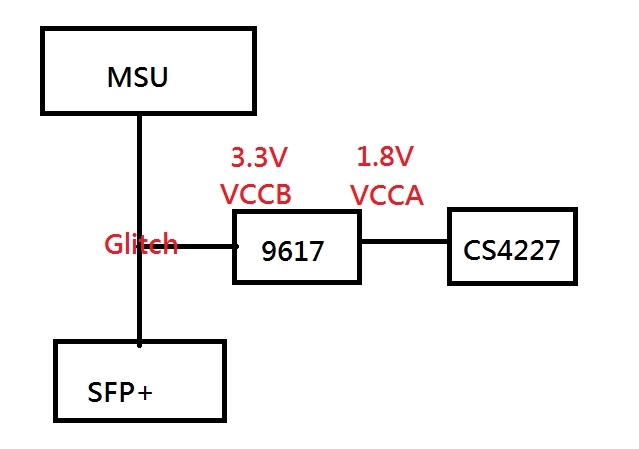

Due to nature of the B-side pedestal and the static offset voltage, there will be a slight overshoot as the B-side

rises from being externally driven low to the 0.5 V offset. The TCA9617B is designed to control this behavior

provided the system is designed with rise times greater than 20 ns. Therefore, care should be taken to limit the

pull-up strength when devices with rise time accelerators are present on the B side. Excessive overshoot on the

B-side pedestal may cause devices with rise time accelerators to trip prematurely if the overshoot is more than

accelerator thresholds. Since the A-side does not have a static offset low voltage, no pedestal is seen on the Aside as shown in Figure 7.

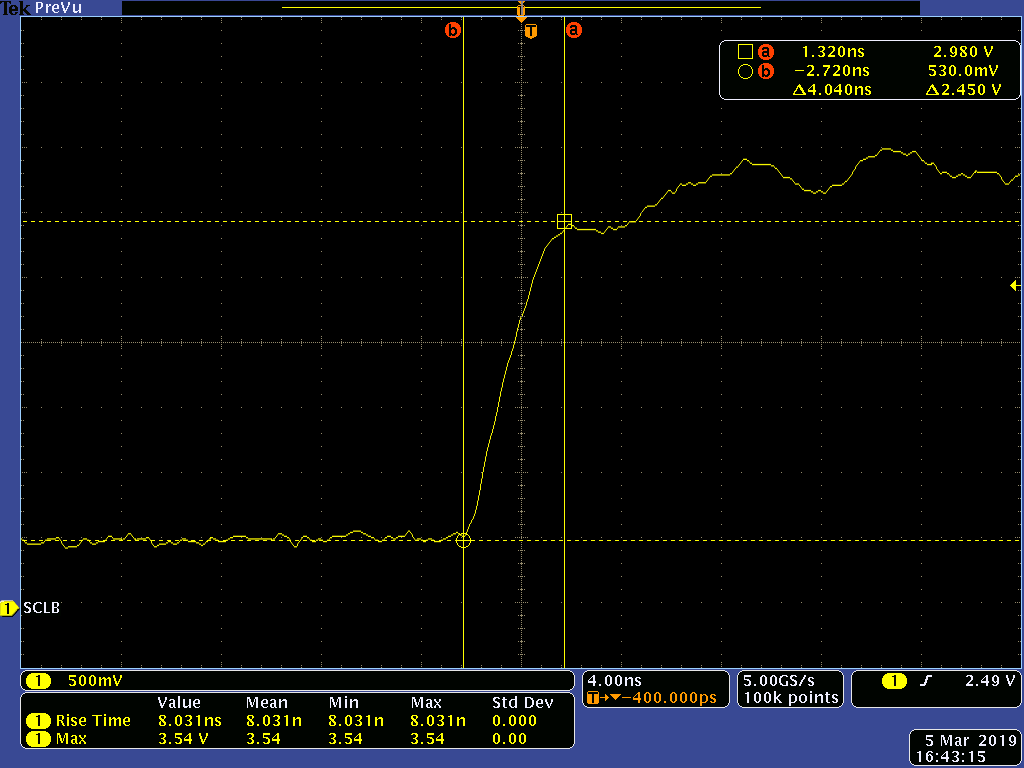

Zoom in to see more detail rising time: