Other Parts Discussed in Thread: SN65DSI84, DSI-TUNER

Tool/software: Linux

Hi,

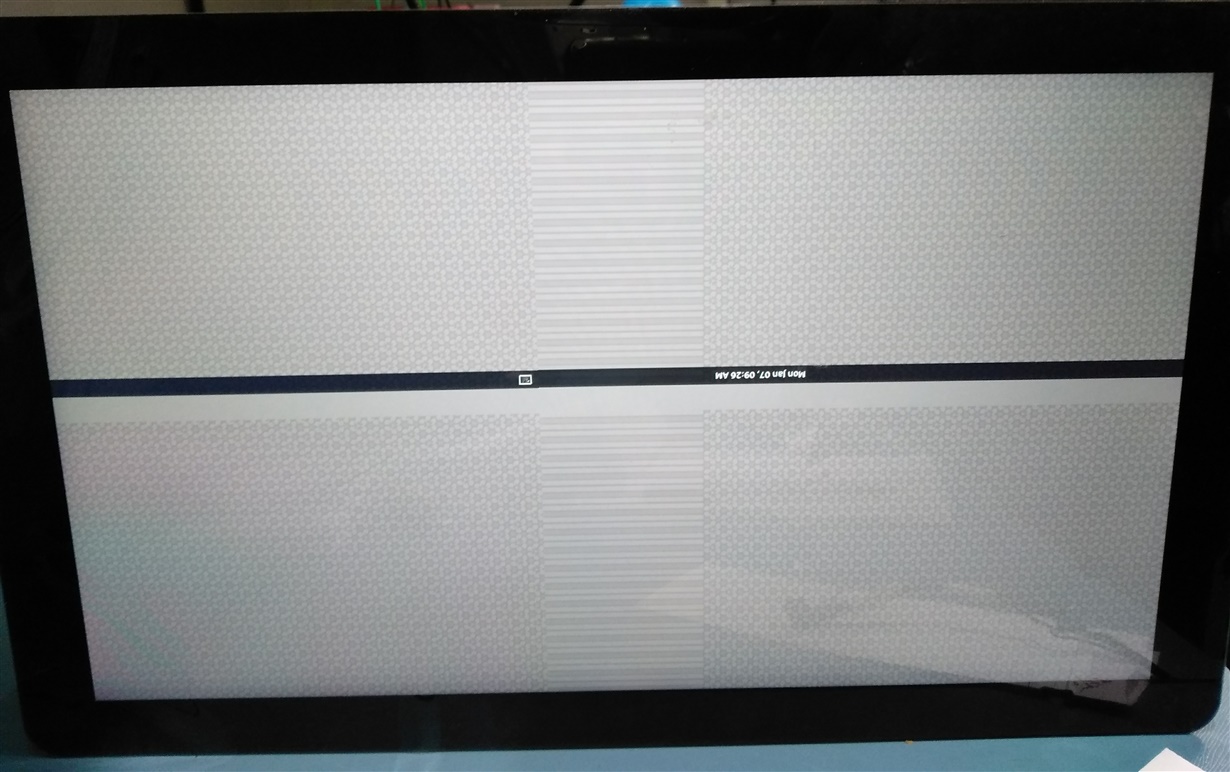

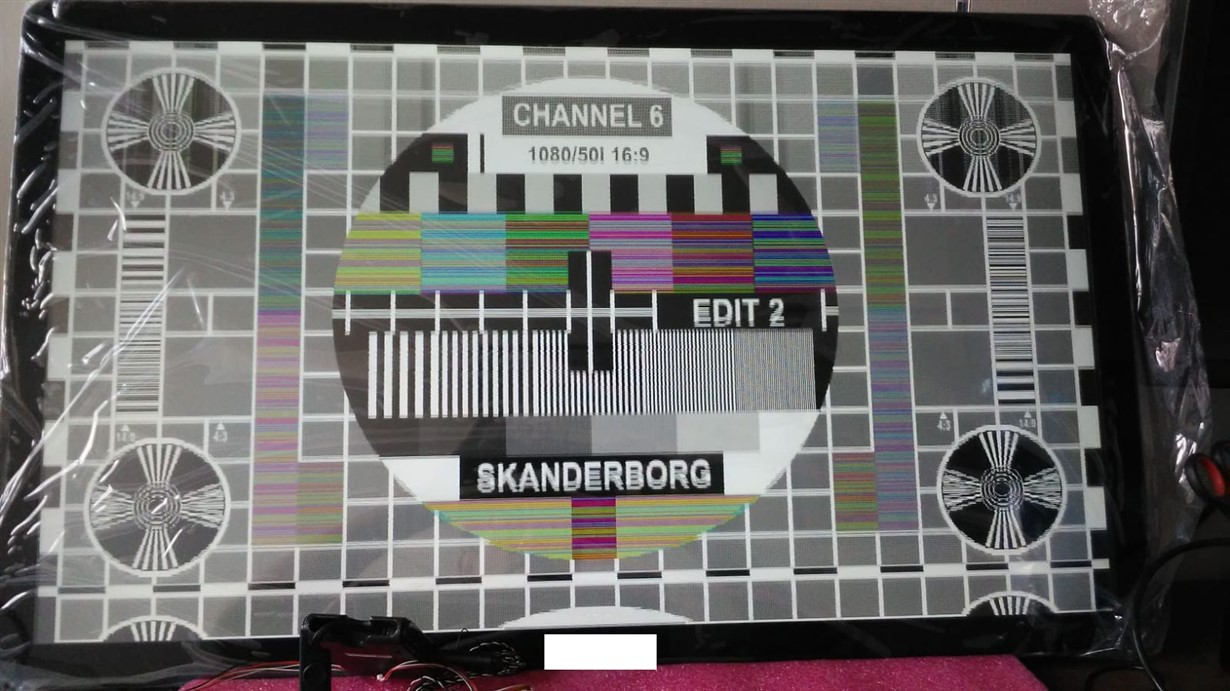

We are using SN65DSI84 in our hardware and we have implemented a MIPI to LVDS converter using this chip set. First we tested the video pattern generation and its working for us.

Now we are trying to display actual data from the mipi interface, but not able to see any data in the display.

So my query is do we need to initialize the SN65 with any MIPI commands from the Host CPU? Our host CPU is i.MX8 and OS is Linux.

Or the I2C initialization enough for the SN65?

Also , could you please share reference code for the SN65DSI84?

Currently we are referring the files panel-sn65dsix.c, sn65dsi8x_i2c.c & fsl-imx8mq-evk-dcss-sn65dsi8x.dts downloaded form the ti form.

Regards,

Bijesh V.M.