Hi,

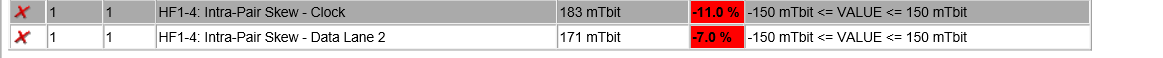

My customer ASUS is using TDP158 in their W700 NOTEBOOK. DGPU output the HDMI2.0 signal, then pass through re-timer to HDMI conn. But there are two failure items in the TDP158 test, could you please help analysis these issues? If they could fix the issues by EQ of the re-timer or adjust the register?

|

Test Plan Information |

|

Test Plan ID: |

R201904170042 |

Report狀態: |

測試中 |

|

測試單位: |

EA |

Current Rev.: |

0.1 |

|

產品線: |

[NB]Notebook |

產品分類: |

Channel |

|

申請類別: |

Other |

Test Plan Type: |

EA |

|

Report Name: |

W700G2T ER EA Measurement Report |

||

|

測試機種類型: |

正式機種:W700G2T |

||

|

屬於系列測試: |

否 |

||

|

ProjectStage: |

ER |

||

|

PCB版本: |

BIOS版本: |

||

|

Driver CD版本: |

|||

|

作業系統: |

None |

||

|

預設完成日: |

2019/05/17 |

實際完成日: |

2019/05/17 |

|

Memo: |

|||

|

ID/Owner |

Description |

Condition |

TestTime |

測試結果 |

Attach List |

|

EA01-22 陸芳 |

[HDMI] HDMI-Electrical 2.0 |

5 |

FAIL |

[W700G2T]1.2_HDMI2.0 EA Report_190514.zip(6852.32kb)(2019/5/14 下午 01:44:58) |