Other Parts Discussed in Thread: MAX3232, , , TRSF3232

Dear all,

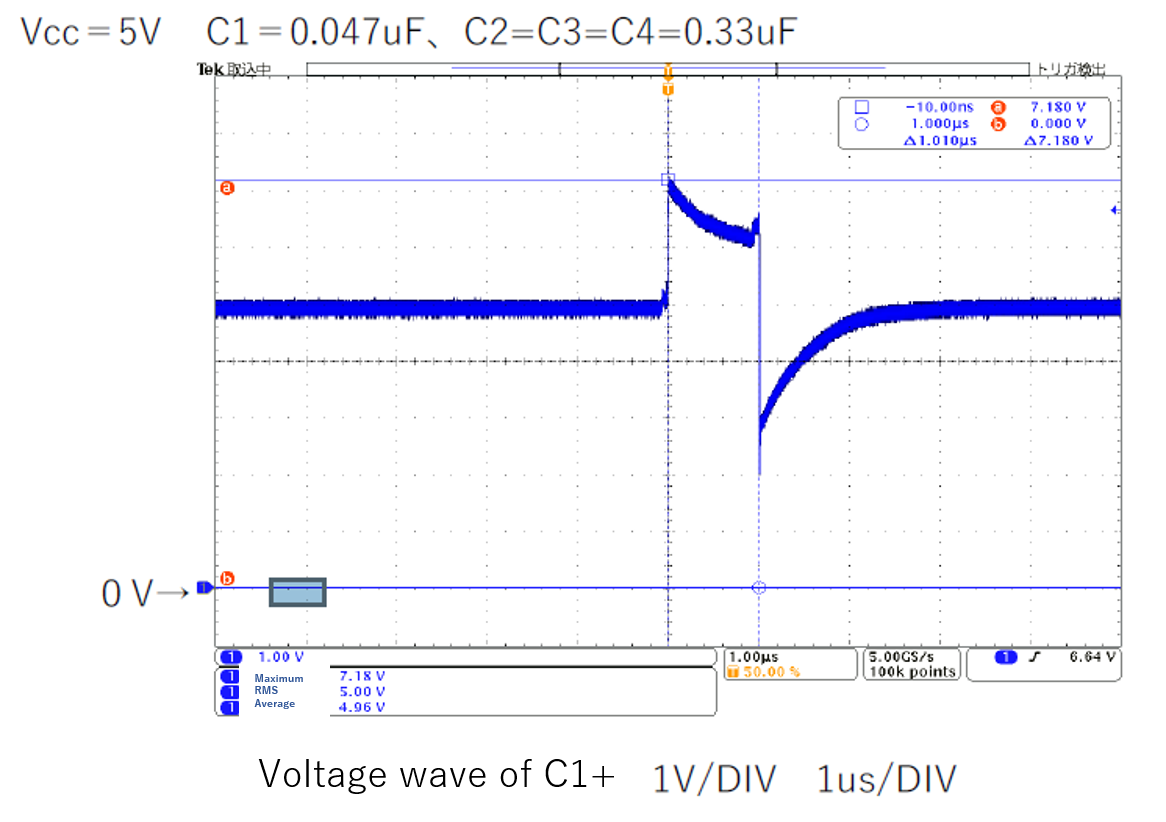

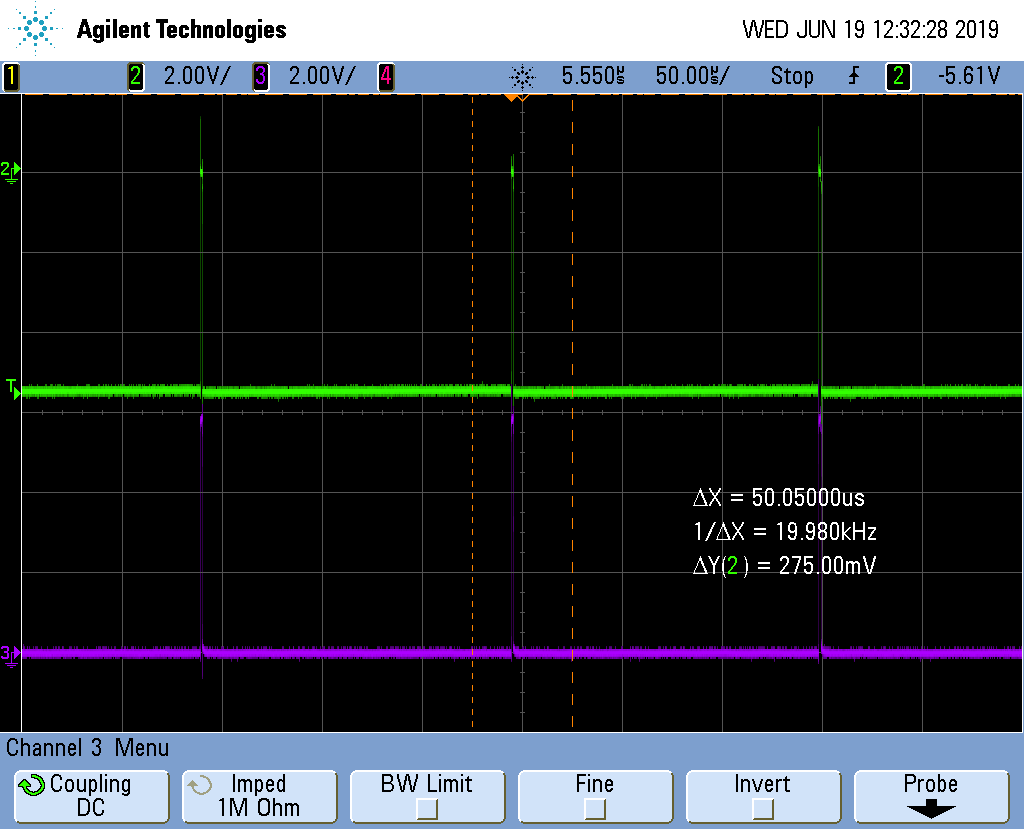

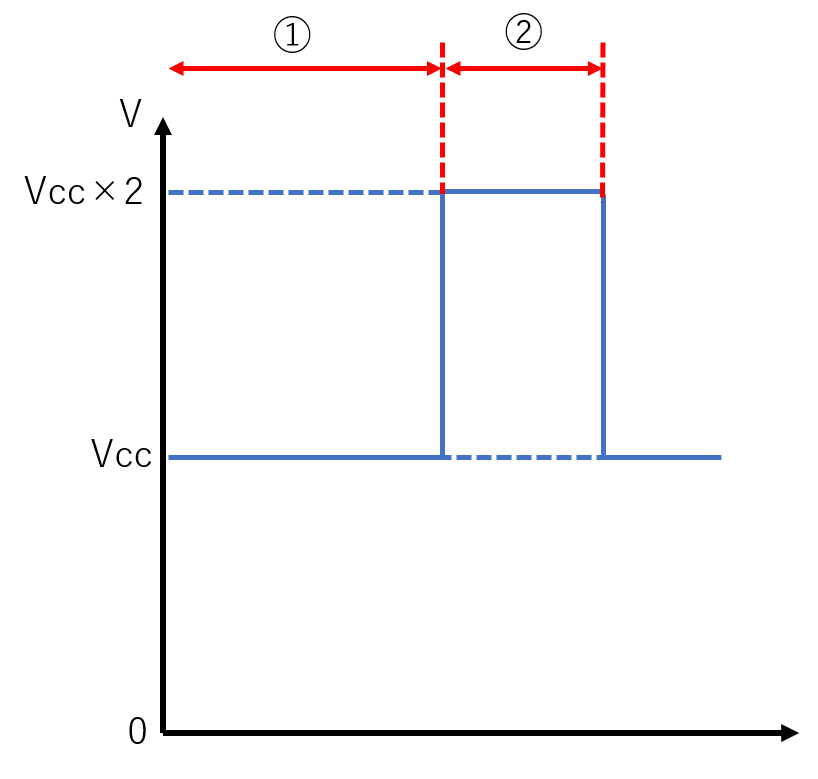

Our customer would like to ask the value of absolute maximum rating for terminals C1 +, C1-, C2 +, C2-.

However, I could not confirm the these value in datasheet.

Could you tell me the maximum rating values for these four terminals?

Best Regards,

Y.Ottey