Hi,

My colleague has posted a question about error code with TLK10232 last week and this problem has been transfered to me now. Our group still have no idea on how to solve this problem.

We are now using the altera FPGA sending data to an xilinx FPGA through optical module and TLK10232. The Intel FPGA send the data to 10G optical module through KR, and then the other board's optical module receives data and send it to TLK10232, lastly TLK10232 send it to the Xilinx FPGA. While error code occurs at the recieving part and can be detected on the Xilinx FPGA.

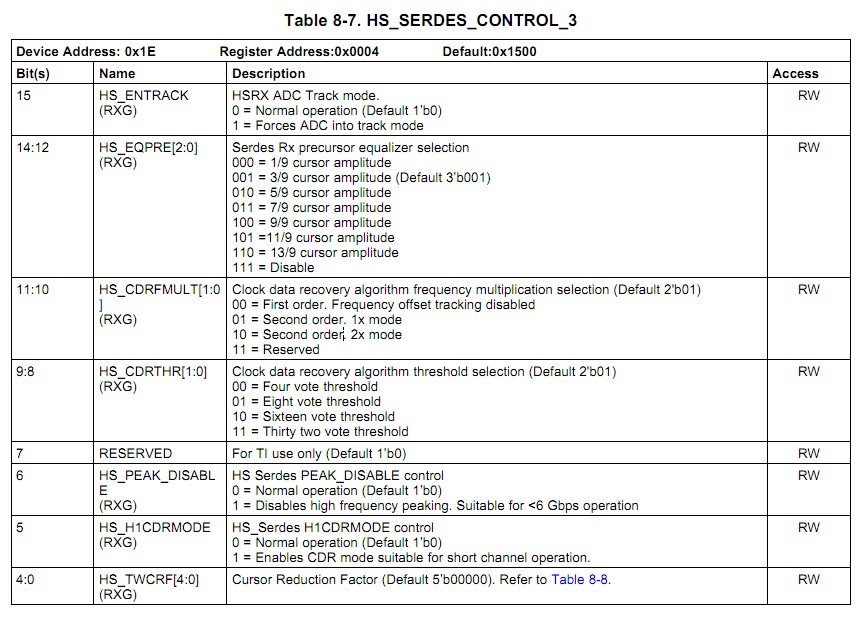

Moreover, during the test last week we find the error code might be related with temperature as the error code would become less while the board has been powered up for a period. We are looking forward to any suggestion to optimize our design and solve this problem.

Thank you very much.