Dear TI-er.

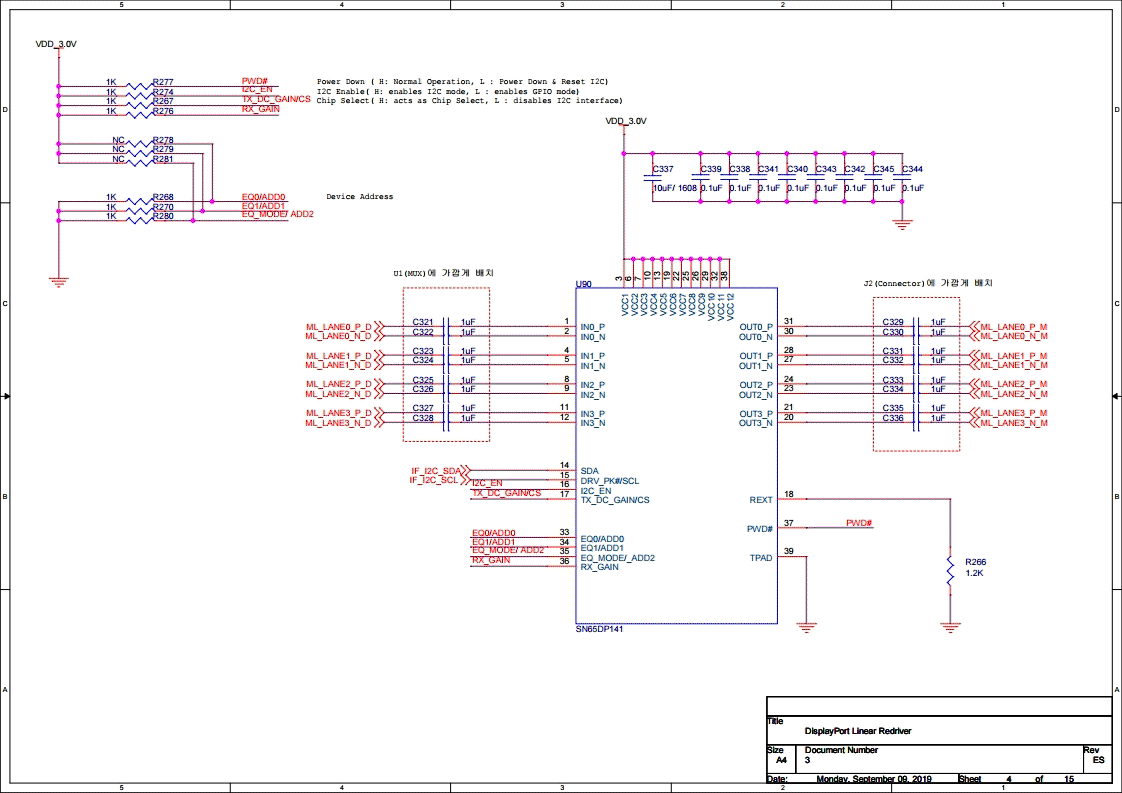

My customer is designed his board to SN65DP141.

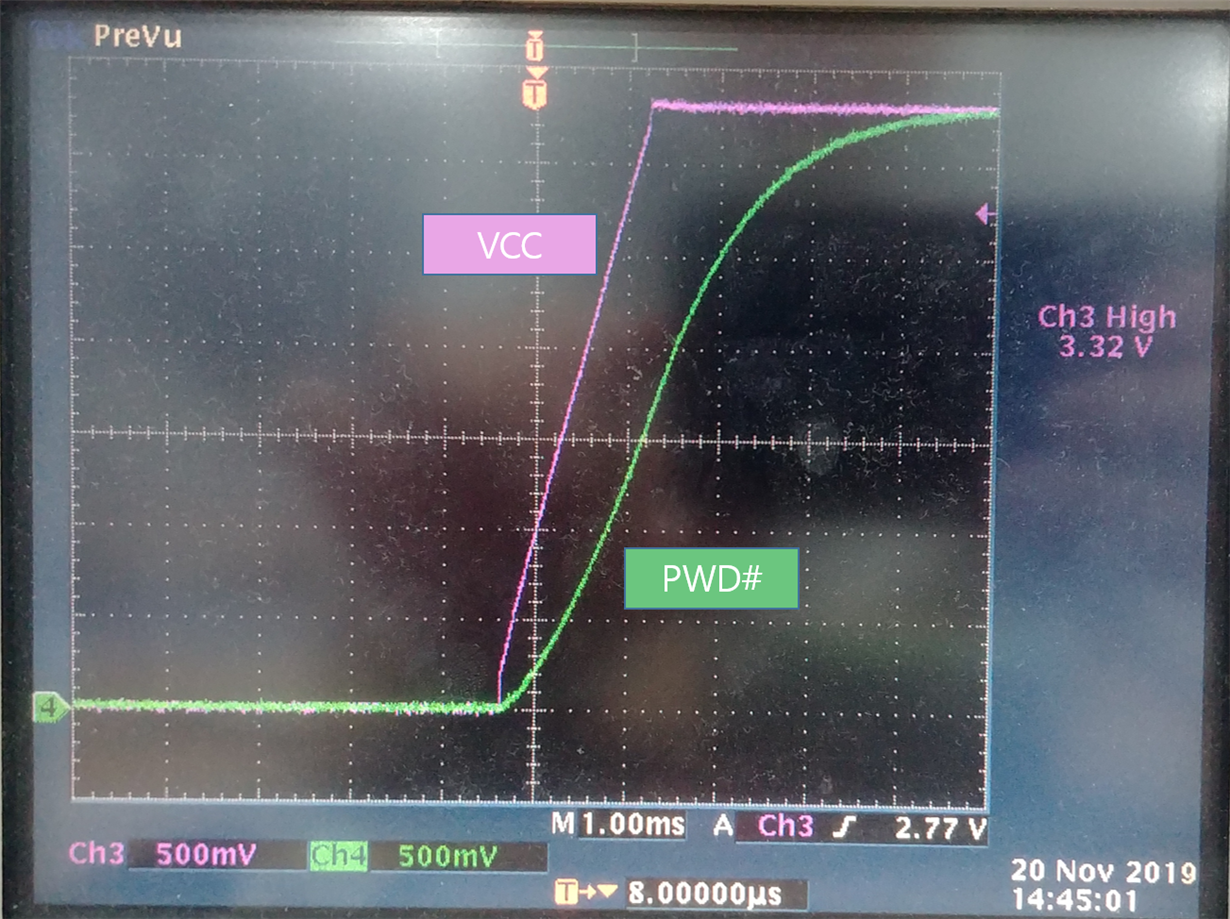

1. He didn't control PWD#(Power down) in the board.

after 1 minute, clearly good operation.

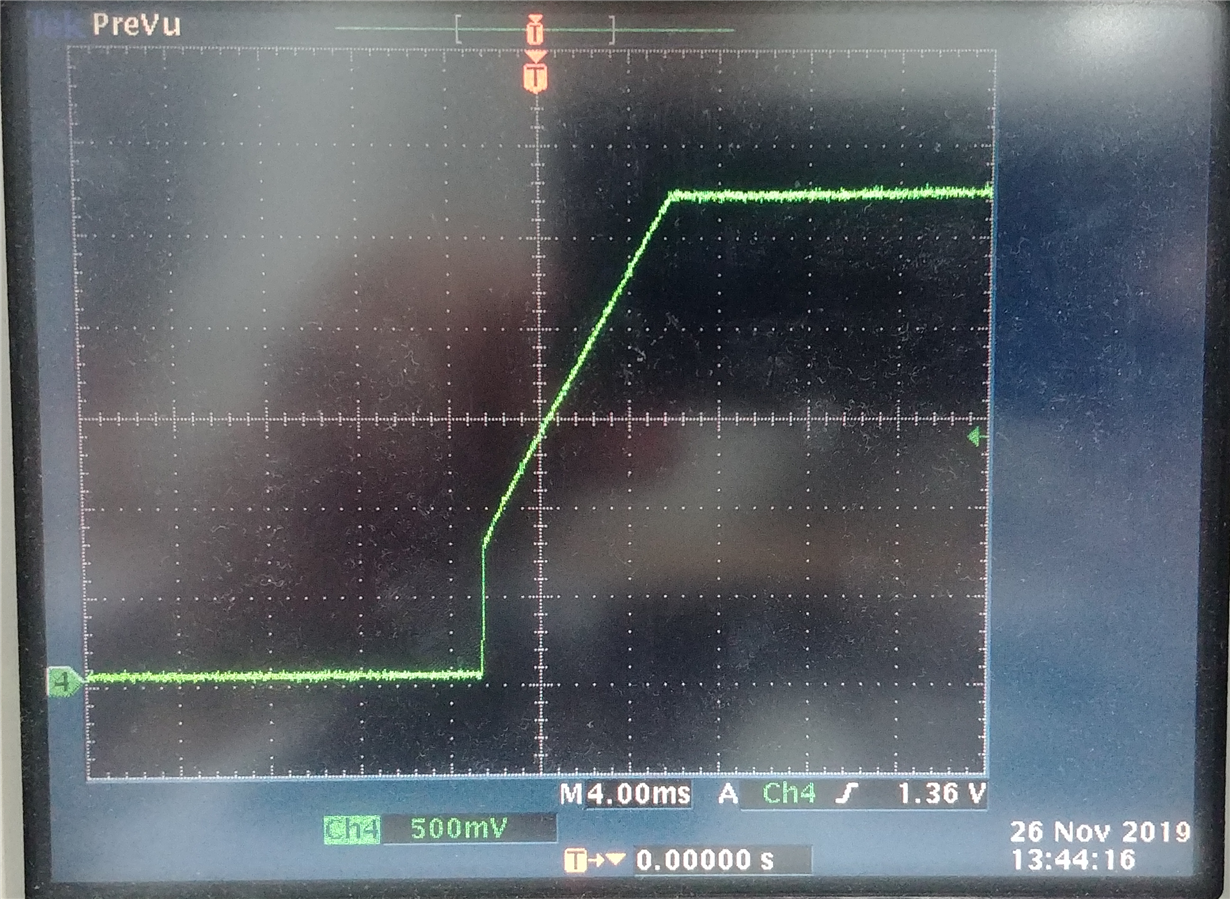

2. He control PWD#=high after 5seconds in power on state.

It is good operation.

Do you know the strage operation ?

plz help me.