Hi,

We have a custom board with Cyclone 10 GX FPGA and SN75DP130. FPGA has DP IP core instantiated in Tx mode (1 lane @ 5.4Gbps) on source path. Standard Dell monitor is used as the sink.

We are not programming any registers and relying on the auto link training to set the equalization and data rate. We could see the HPD_SNK from the monitor going high, but its is not reflecting on HPD_SRC output. Also no activity on AUX_SRC interface. The device is out of reset and responds to I2C read commands by returning non-zero values. These register values keep changing over time, so SN75DP130 is trying some thing.

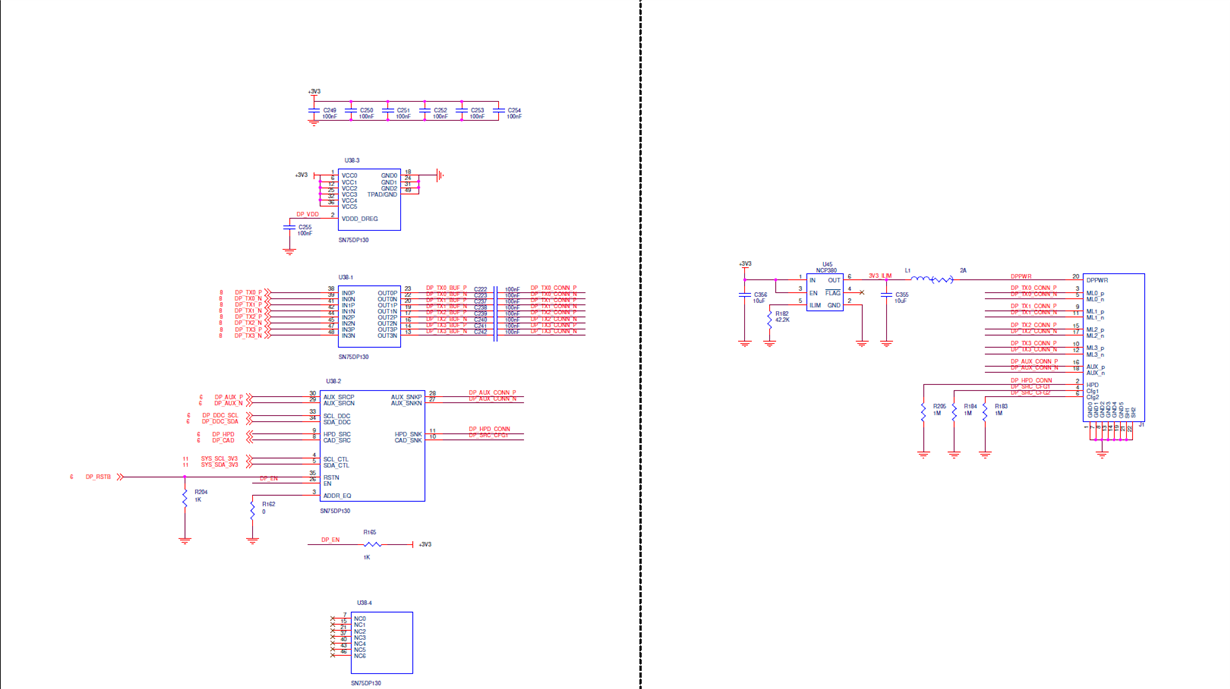

Some of the Device Pin Connections:

EN signal is connected to 3.3v supply through a 1K pull-up resistor.

CAD_SNK is connected to connected to cfg1 pin of DP Connector and has external 1M resistor to ground.

What could be blocking SN75DP130 from progagating HPD signal from SNK interface to SRC interface? Does the device propagate HPD signal only after successful link training?

Do we need to check any specific registers or device pins to understand the problem?

Thanks