Hello,

I am using the remote GPIO over back channel function (FPD-III) to transmit a 60 Hz frame sync signal from the DS90UB934 deserialer's GPIO0 pin to GPIO0 of the 935 serializer, and then to send that signal to the image sensor. This mode is described as the "Extenal FrameSync Control" function in the 934 datasheet. The SerDes system uses DVP Coax mode.

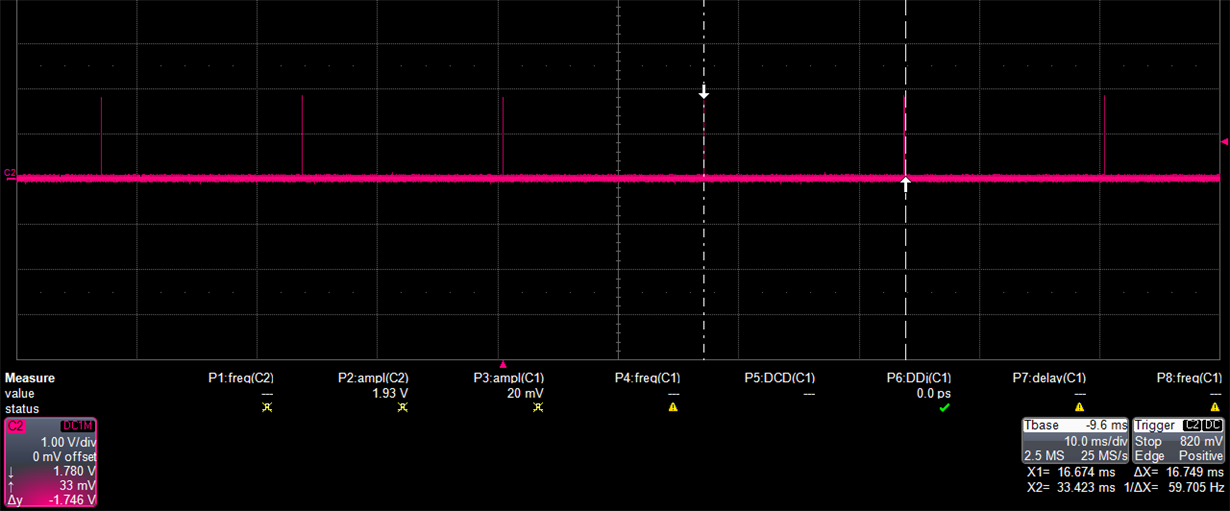

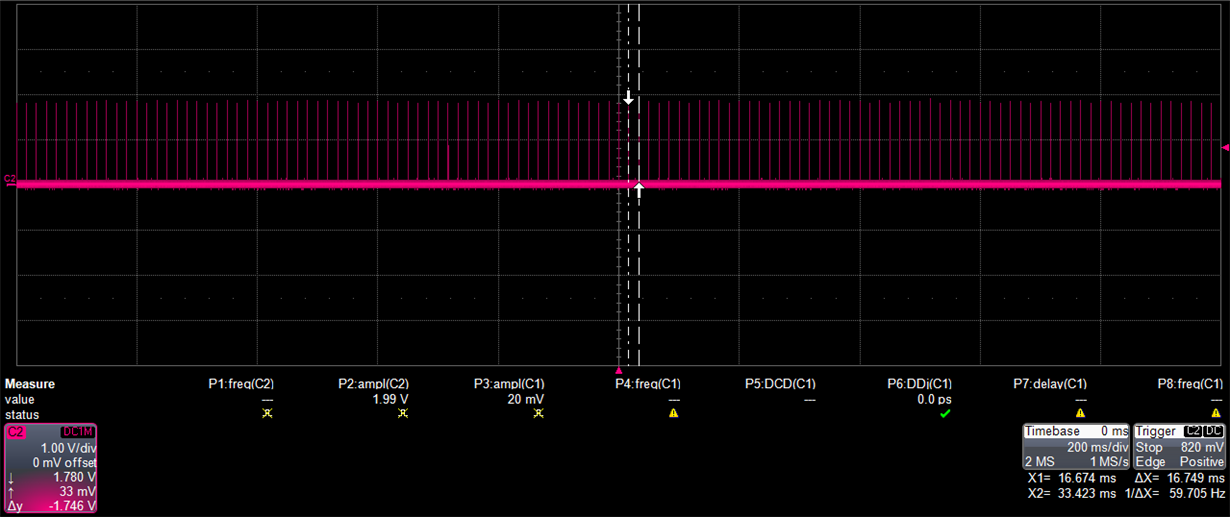

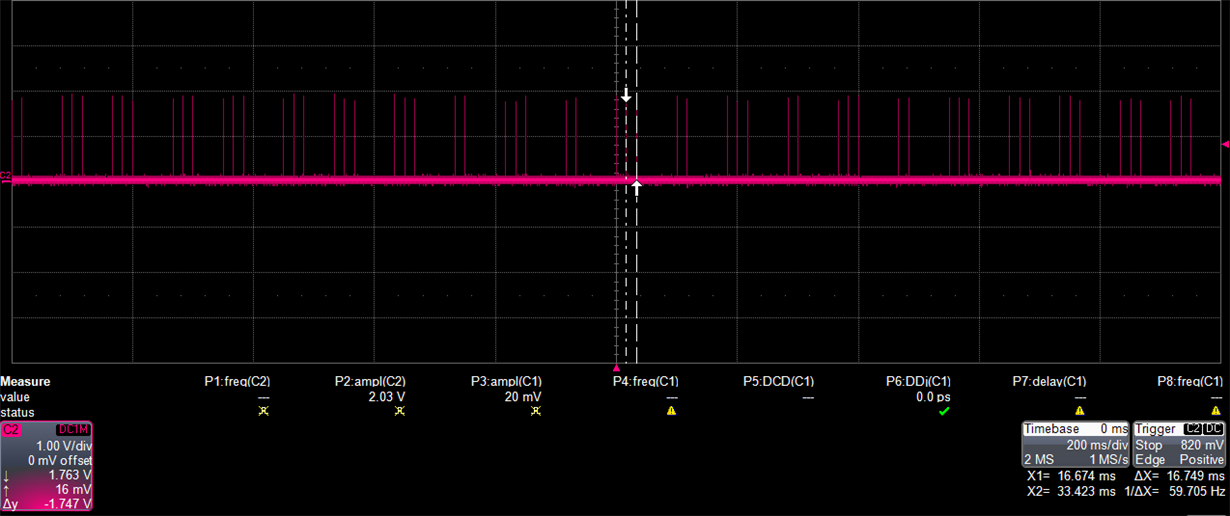

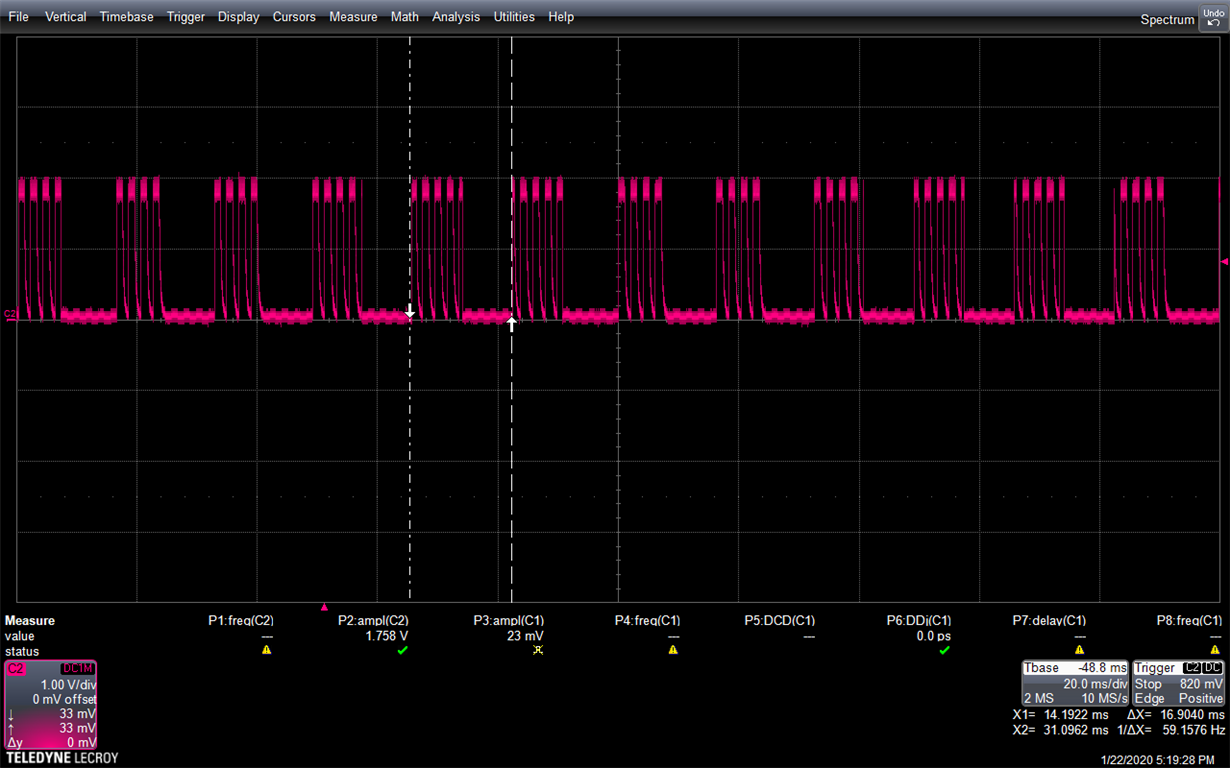

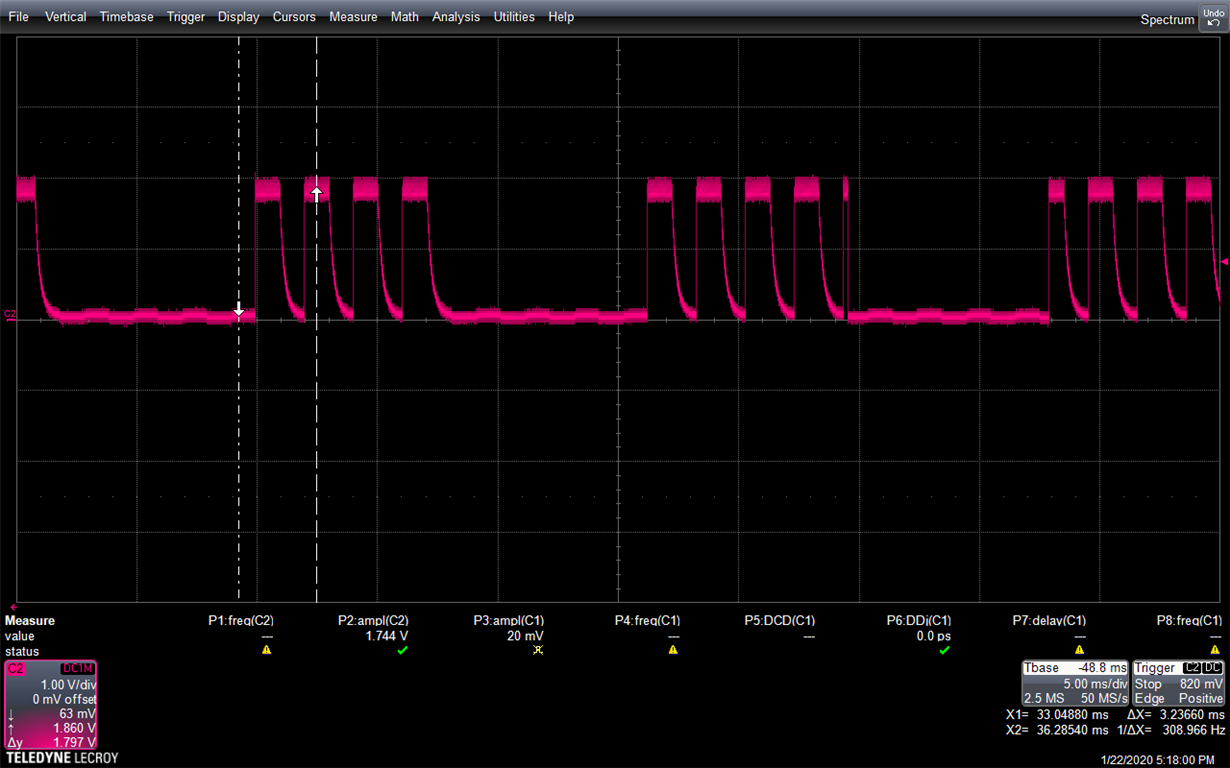

The issue is that the signal coming out of the serializer is missing frame sync pulses, and those that do come out are of varying length. Whereas the pulses come out of the Des at 60 Hz and are always 15us, most Ser pulses are 12.4us, some are 24.8us, and some are 9.7us. See scope captures below:

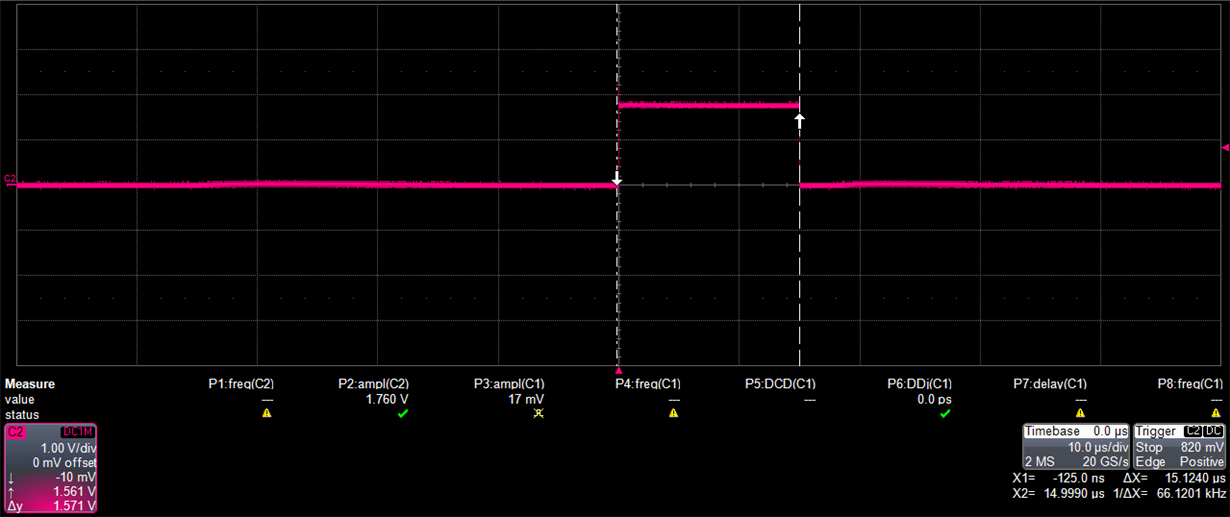

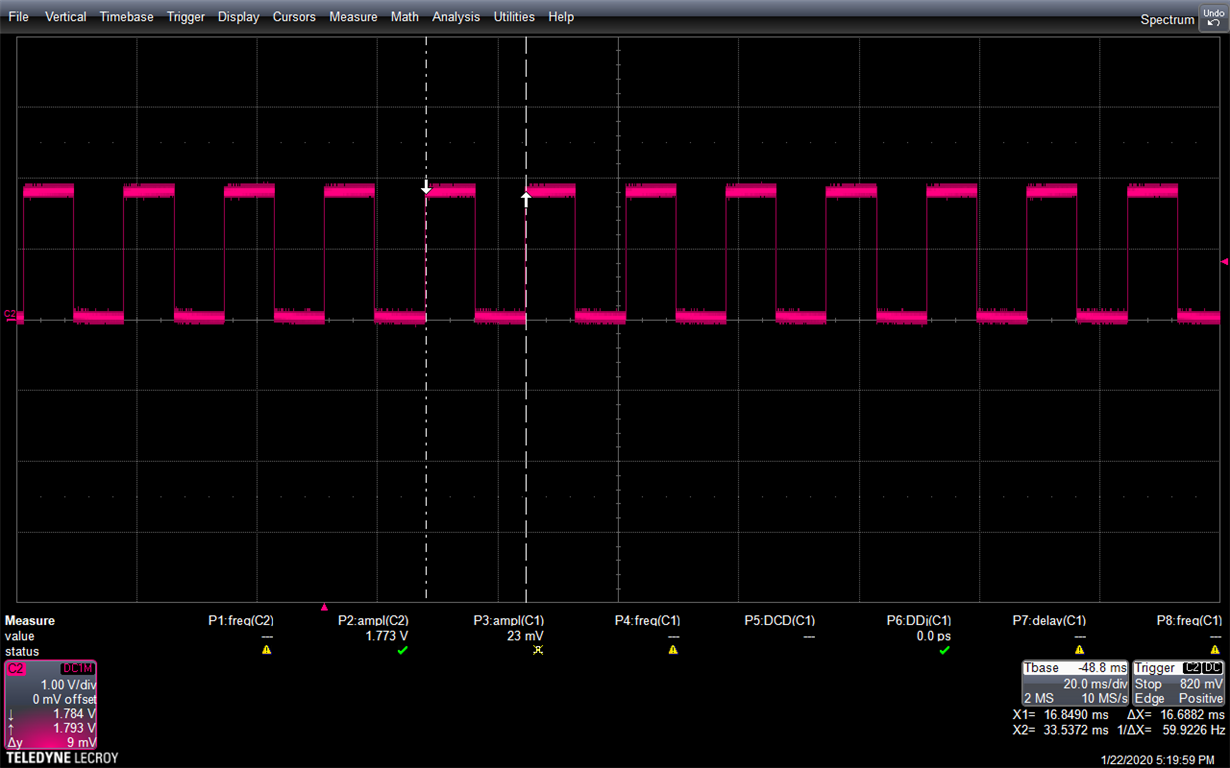

Input waveforms (to Des GPIO0):

Output waveforms from (Ser GPIO0):

The input FrameSync pulses last for 15us, and the DVP mode's 83.5 KHz sampling rate implies sampling occurs every 12us. Why is the system missing so many samples?

I need to a frame sync to appear at a consistent 60 FPS. Outputting pulses of incorrect length at seemingly random intervals won't work for my video project.

Has anyone dealt with this issue before? Any advice would be greatly appreciated.

Thanks.

Regards,

Sam Shafer