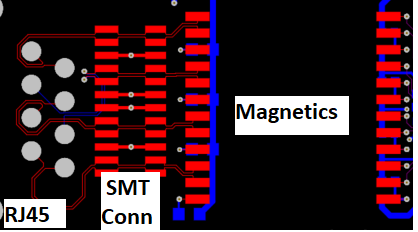

I am working on a custom board with three DP83867IR parts on it, using the Pulse HX5008NL magnetics and a Stewart SS-7488S-YG-PG4-BA RJ45 connector. It is currently failing the 1000base-T Peak Voltage tests for points A and B - the peaks measure at about 565mV (the minimum required is 670mV) on all three channels. The mask tests all seem to pass. The layout guidelines in the data sheet have been followed as closely as possible. I've searched through the E2E boards for answers, but didn't find anything definitive. The PHY is outputting the proper mode-1 waveform with the same peak voltages on all 4 pairs. Any insights you can provide will be appreciated.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.