Hello,

I got a question about the auto MDIX negotiation:

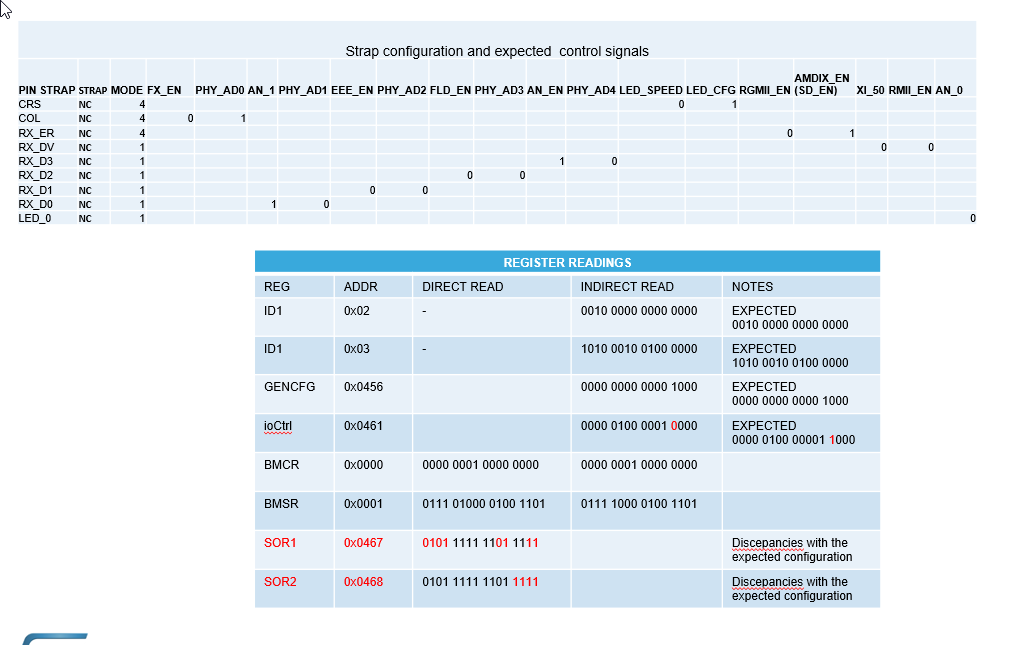

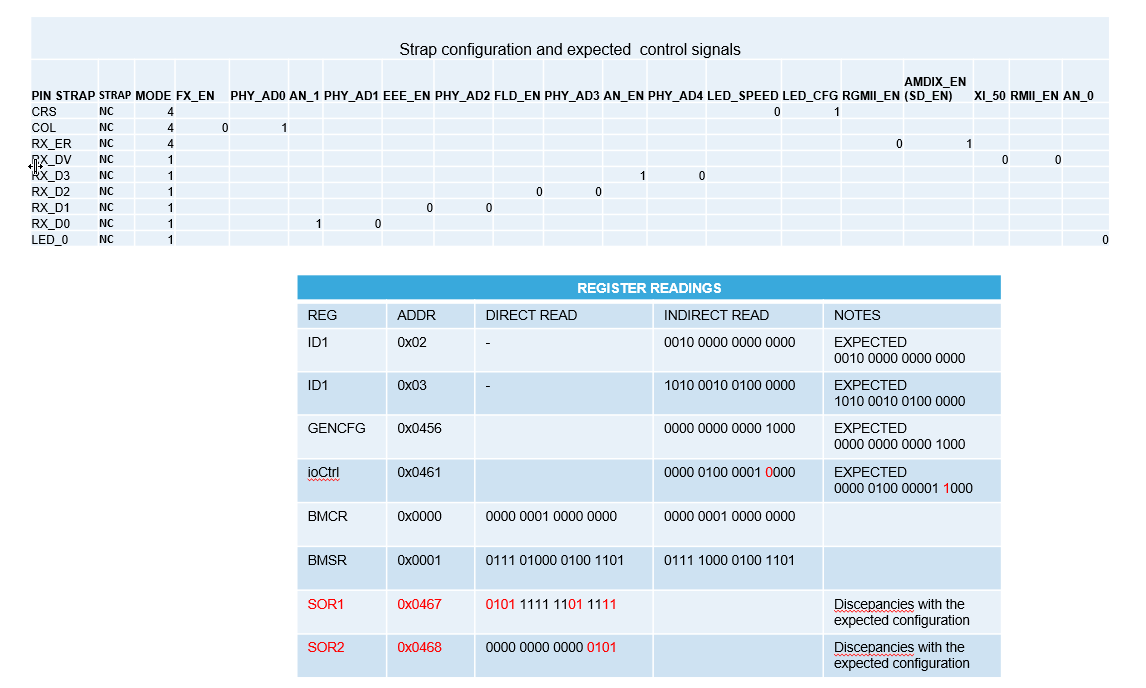

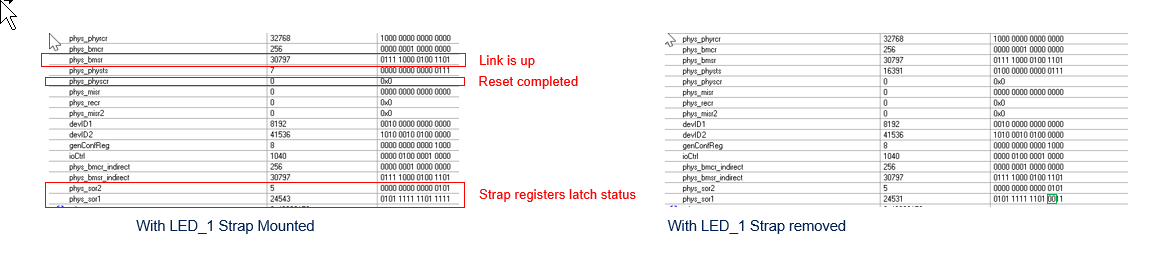

In the system I am working with the PHYS DP83822I is strapped in default mode with floating RX_ER --> AMDI_EN=1.

Now I expect that in this condition register PHYCR (0x19) bit 15 to be set.

What I see is that register 19 is all zero. Is that correct?

the prototype I'm working with is directly connected to my PC with a straight cable and it can communicate. What am I missing?

Another question.

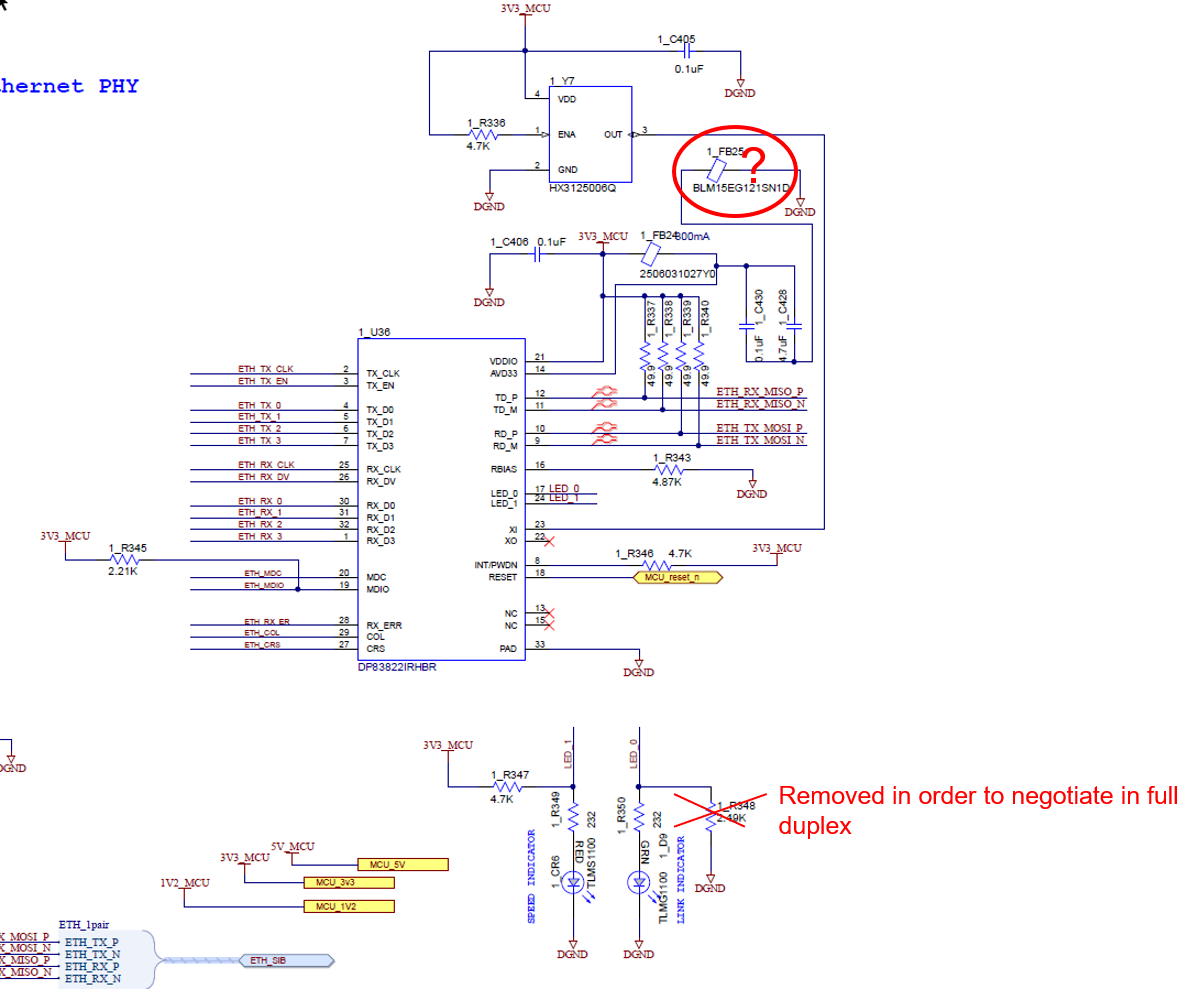

For layout reasons we might need to swap TDP-TDM with RDP-RDM from the phys to the connector. This would result in the phys to treat the straight cable as a twisted one and vice versa. Can you see issues for this unconventional solution?

Best regards,

GZ