Other Parts Discussed in Thread: DS90UB949A-Q1, DS90UB914A-CXEVM, DS90UB913A-CXEVM, TIDA-020003, DS90UB949-Q1

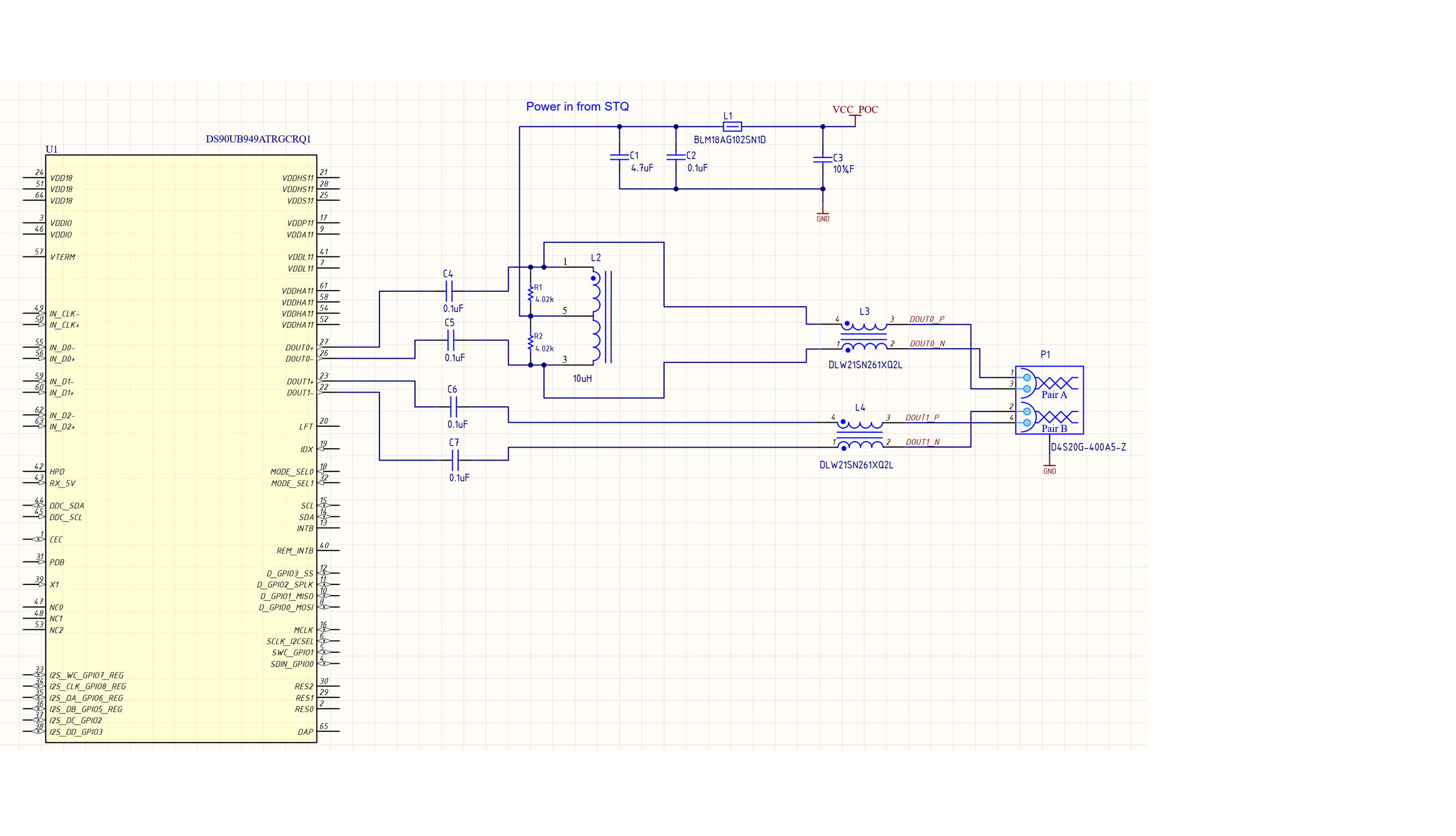

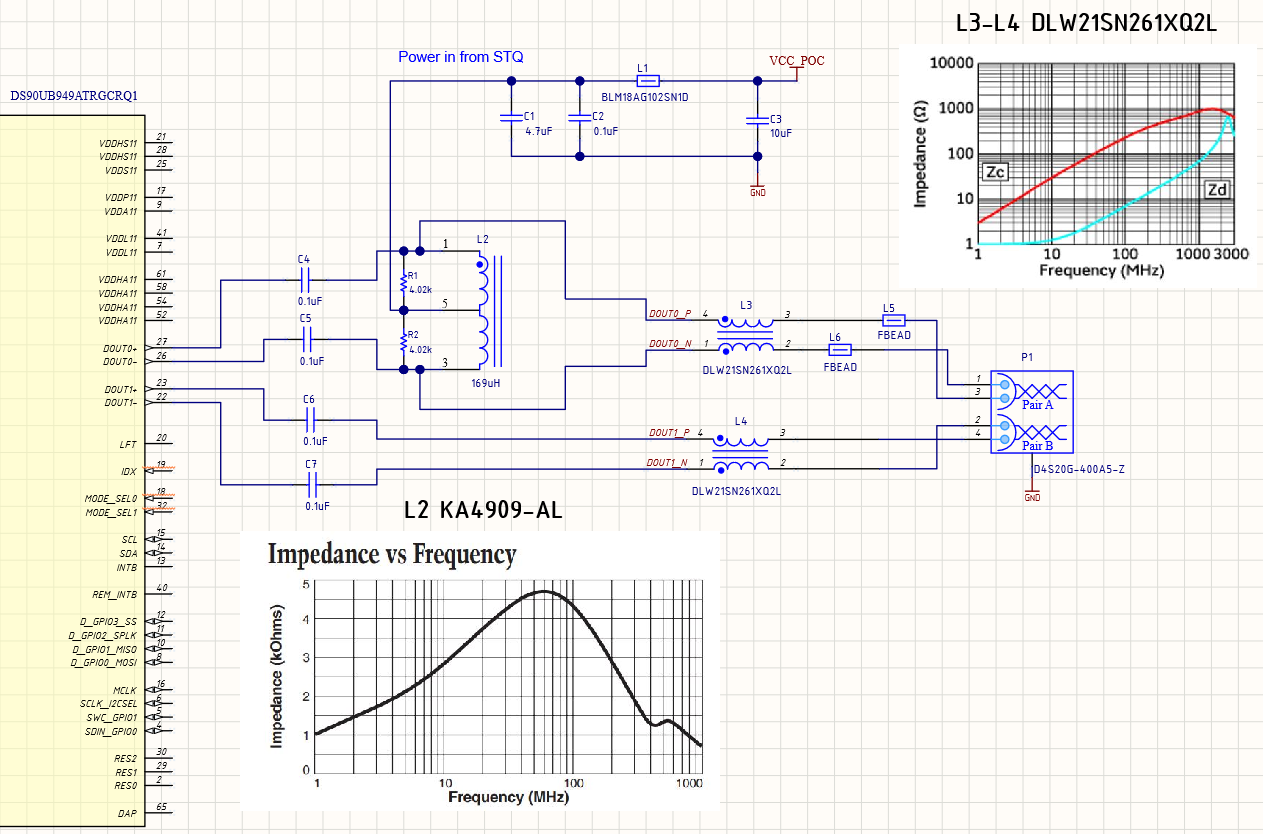

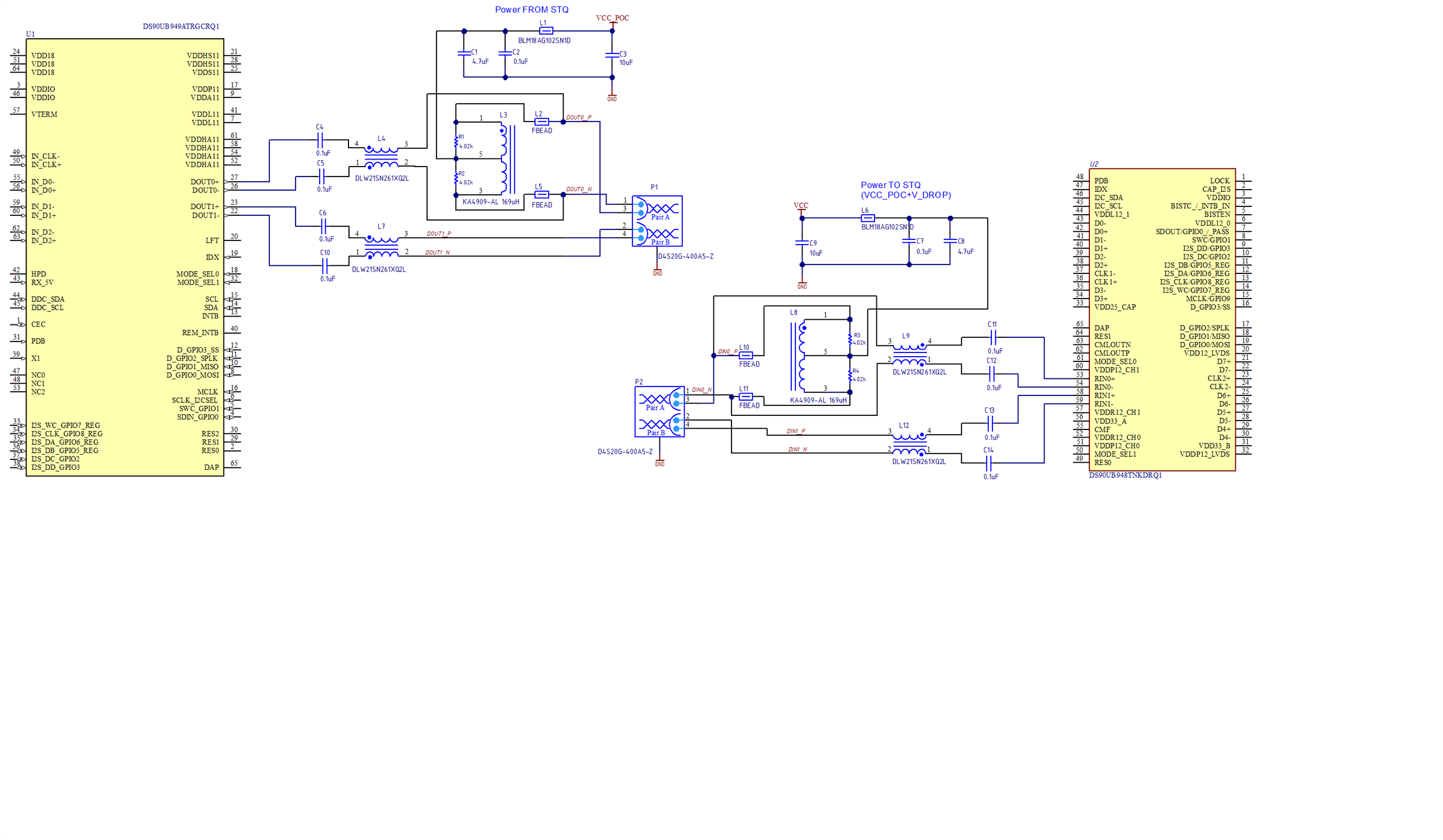

We're going to use DS90UB949A-Q1 and DS90UB948-Q1 pair in dual link mode with STQ cable (6 meters) for PCLK up to 192MHz.

It's desirable to implement power over cable.

I have following questions:

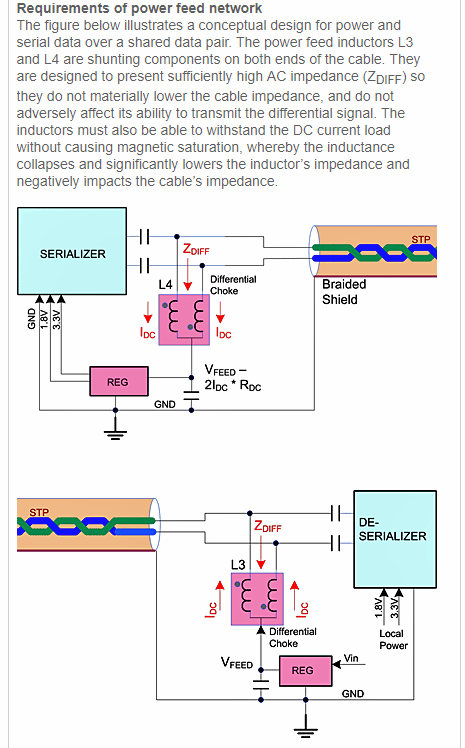

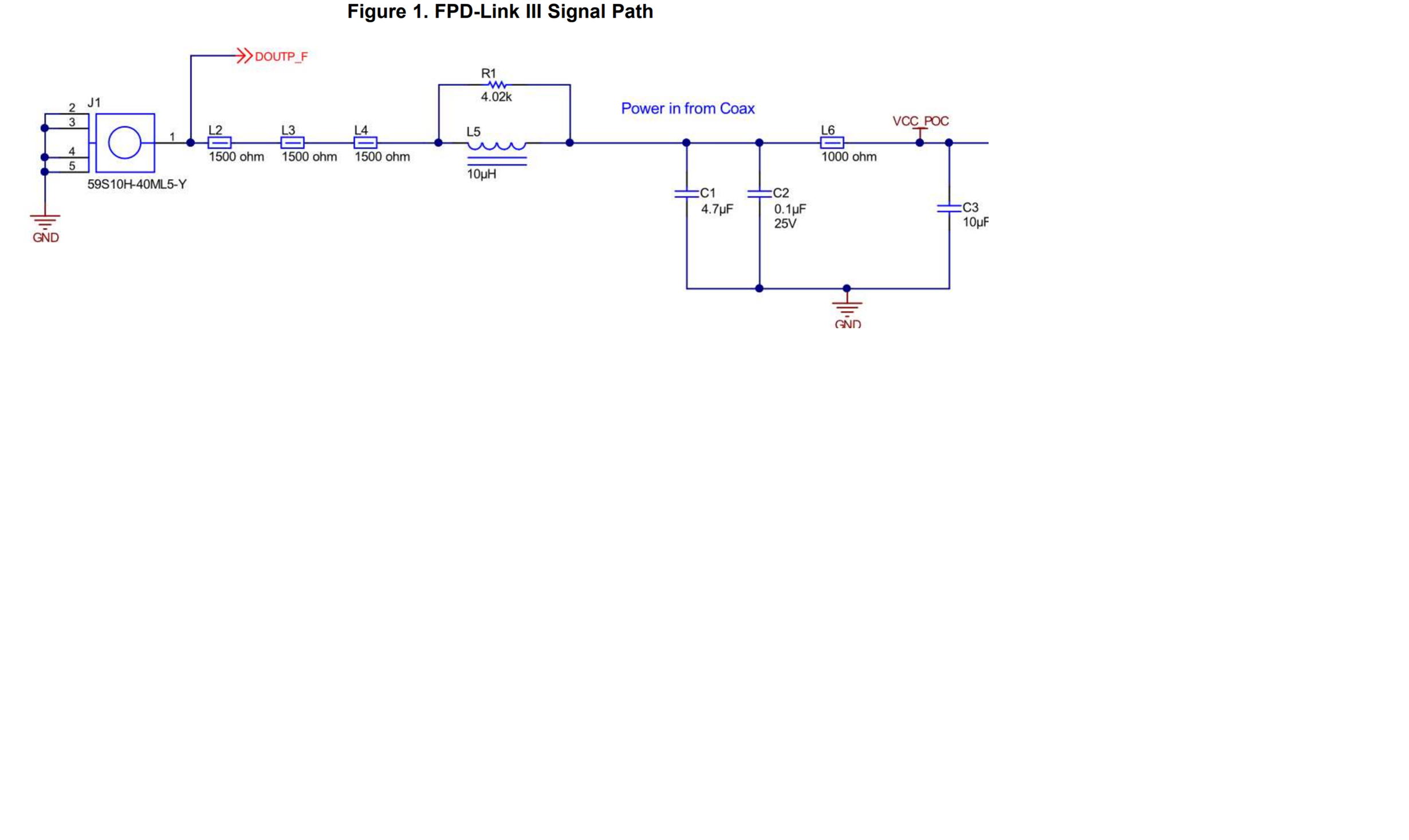

1. Is it possible to use concept of power over STP described in DS90UB913A-CXEVM & DS90UB914A-CXEVM evaluation modules in case of dual link over STQ for DS90UB949A-Q1 and DS90UB948-Q1 pair?

If yes, should power be translated over each twisted pair inside STQ? or just one?

2. If i.1 is not working solution, can I switch to dual link with 2 coax and PoC?

Thank you.