Hi TI Team.

We are using DS90UB936-Q1 deserializer. We have 1 MIPI lane connected with our host processor. The resolution is 1280 x 720 at 30fps.

We want to generate test pattern on the deserializer. Below are the deserializer register settings done for this:

Reg:0x20 | Value: 0x30 # Forward Control Disabled for RX0 and RX1

Reg:0x1f | Value: 0x02 # CSI PLL : 1.6 Gbps

Reg:0x33 | Value: 0x33 # CSI enable, Continuous clocks, Lane Count=1

Reg:0xB0 | Value: 0x01 # Indirect Pattern Gen Registers - Select Pattern Block

Reg:0xB1 | Value: 0x01 # PGEN_CTL

Reg:0xB2 | Value: 0x01

Reg:0xB1 | Value: 0x02 # PGEN_CFG

Reg:0xB2 | Value: 0x33

Reg:0xB1 | Value: 0x03 # PGEN_CSI_DI

Reg:0xB2 | Value: 0x24

Reg:0xB1 | Value: 0x04 # PGEN_LINE_SIZE1

Reg:0xB2 | Value: 0x0F

Reg:0xB1 | Value: 0x05 # PGEN_LINE_SIZE0

Reg:0xB2 | Value: 0x00

Reg:0xB1 | Value: 0x06 # PGEN_BAR_SIZE1

Reg:0xB2 | Value: 0x01

Reg:0xB1 | Value: 0x07 # PGEN_BAR_SIZE0

Reg:0xB2 | Value: 0xE0

Reg:0xB1 | Value: 0x08 # PGEN_ACT_LPF1

Reg:0xB2 | Value: 0x02

Reg:0xB1 | Value: 0x09 # PGEN_ACT_LPF0

Reg:0xB2 | Value: 0xD0

Reg:0xB1 | Value: 0x0A # PGEN_TOT_LPF1

Reg:0xB2 | Value: 0x04

Reg:0xB1 | Value: 0x0B # PGEN_TOT_LPF0

Reg:0xB2 | Value: 0x1A

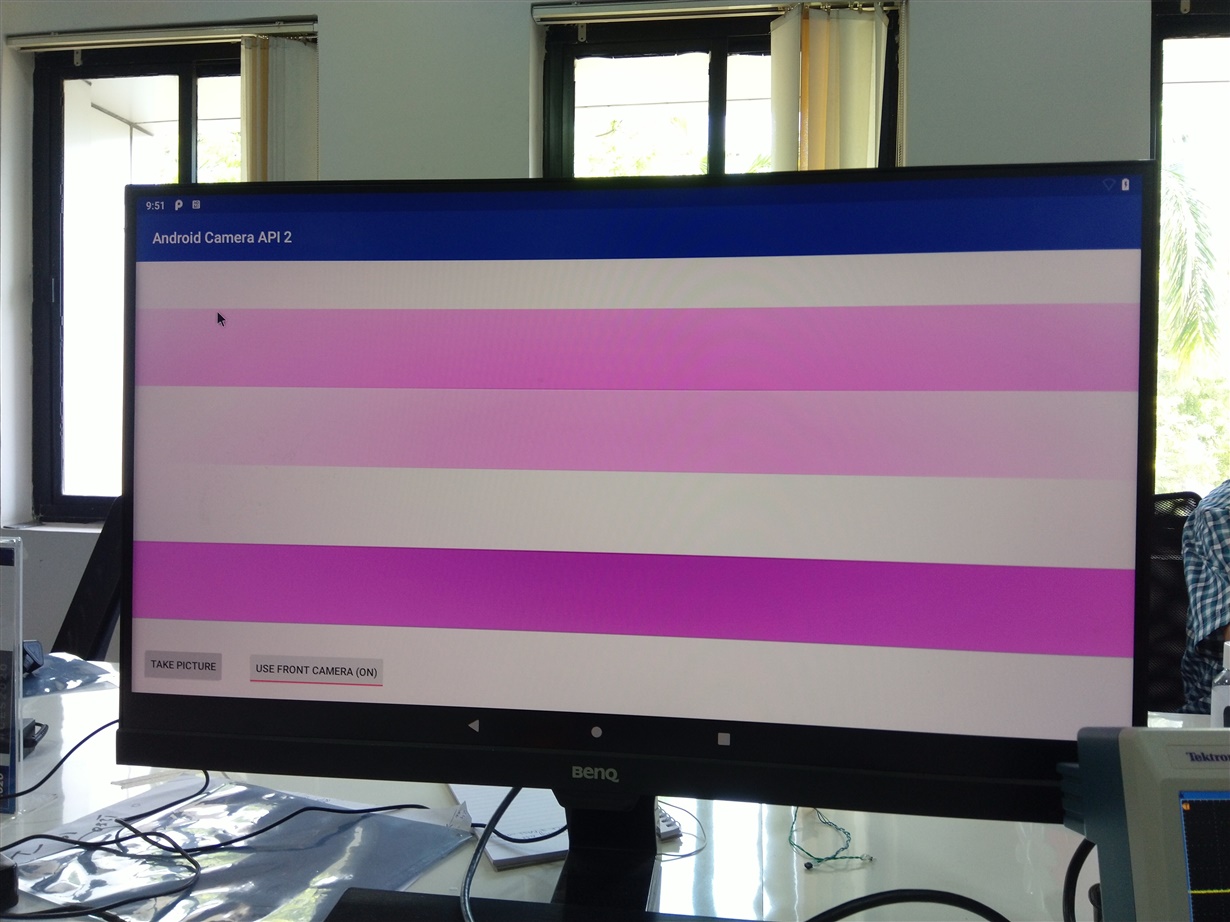

Despite of this, we are not getting any output on our host processor. (The MIPI lines on the host are working)

> Are the register settings correct ?

> What could be the probable reasons for not getting the output?

Regards,

Khilav