Other Parts Discussed in Thread: DP83822I

Hi team,

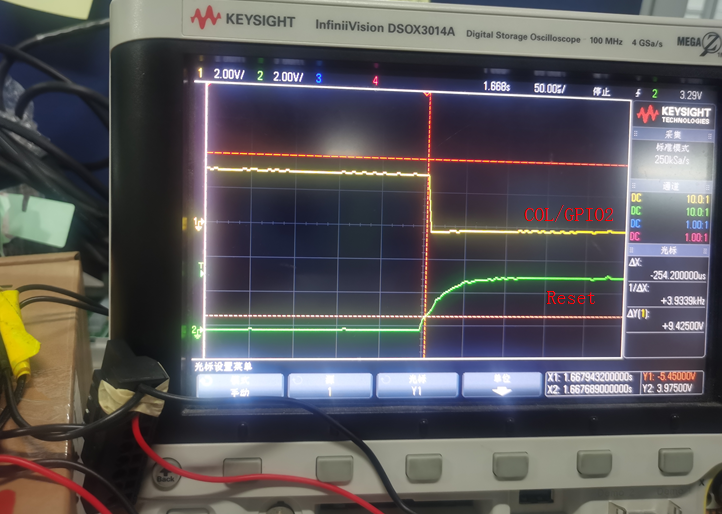

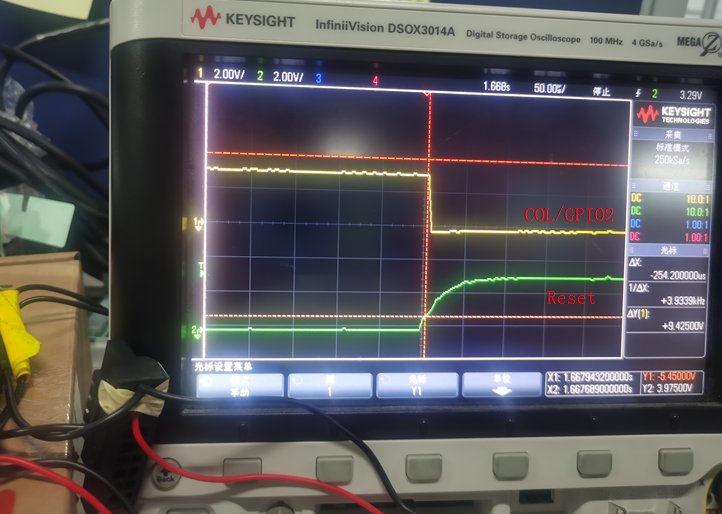

My customer use DP83822I and found an issue. For bootstrap mode COL pin, customer use default mode -- MODE 4 , without external pull up or pull down. So based on below Table 10, the voltage of COL shall be high VDDIO . But customer measured the voltage of COL, and found during reset stage, the COL is High, but after reset de-assert, the voltage of COL become and keep low. So what's reason?