Other Parts Discussed in Thread: DS92LX1621

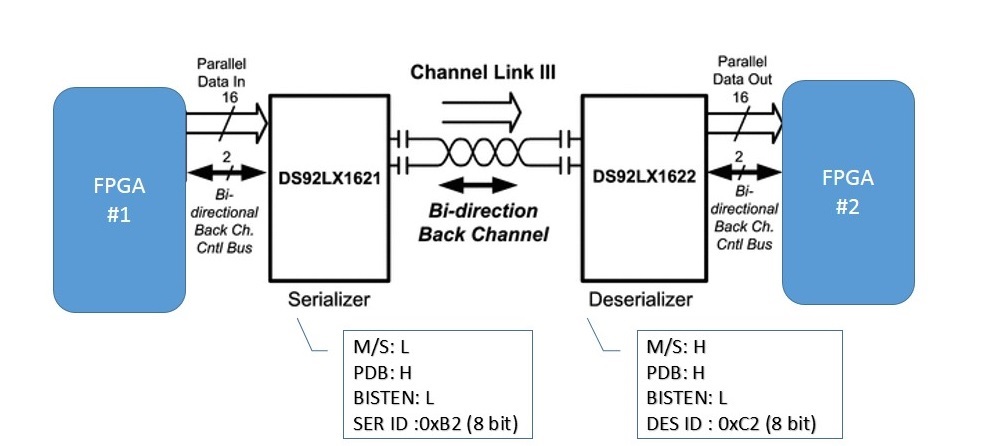

I am trying to establish a very simple communication link between DS92LX1621 & DS92LX1622.

I have no plan to have any I2C remote device (e.g. camera) and not intrested in "I2C Pass Through" feature.

i just need to send some parallel data (16 bit) through the diferantial link of DS92LX1621 & DS92LX1622.

here is a scheme :

which registers shall be programed for this comunication?

here is what i have implementer so far:

=============

SER ID = 0xB2 (8 bit addr)

DES ID = 0xC2 (8 bit addr)

=============

1)Perform Remote Wake Up Sequence ==> Datasheet page 34 ,REMOTE WAKE UP section

Write 0xC0 to register 0x26 of DS92LX1622

Write 0x04 to register 0x01 of DS92LX1622

Write 0x00 to register 0x26 of DS92LX1622

2)Set DES to normal operation mode ==>Datasheet page 24, Table2

Write 0xE0 to register 0x27 of DS92LX1622

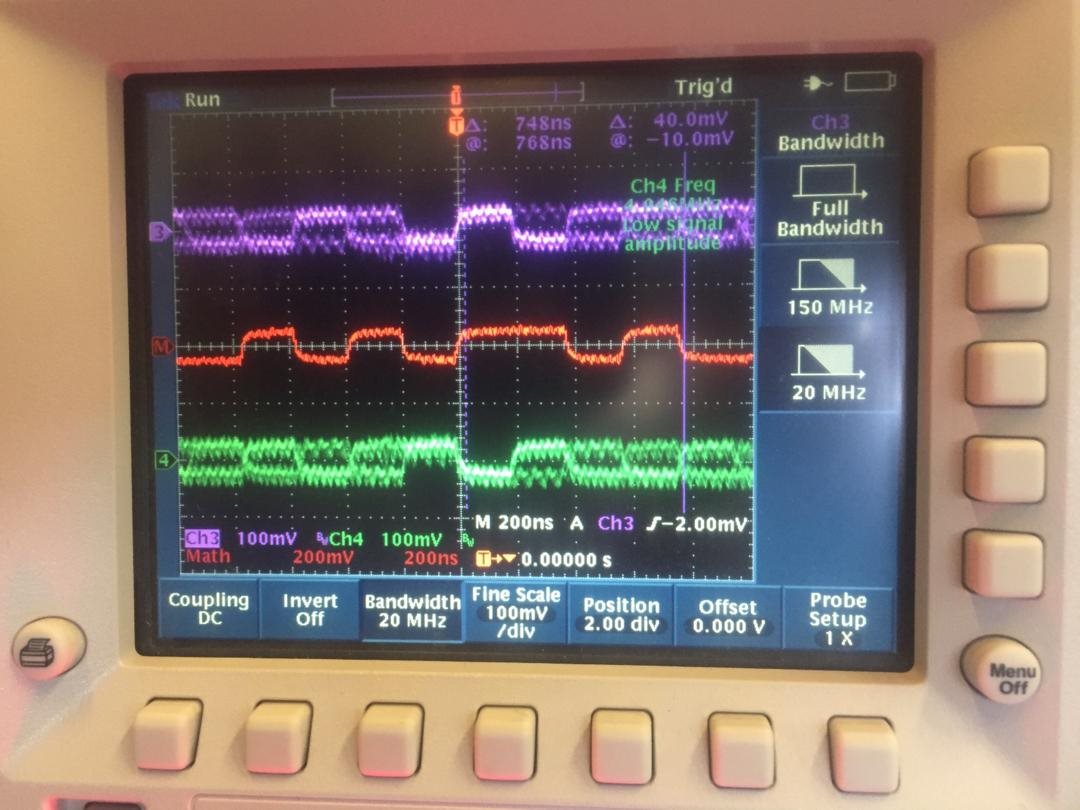

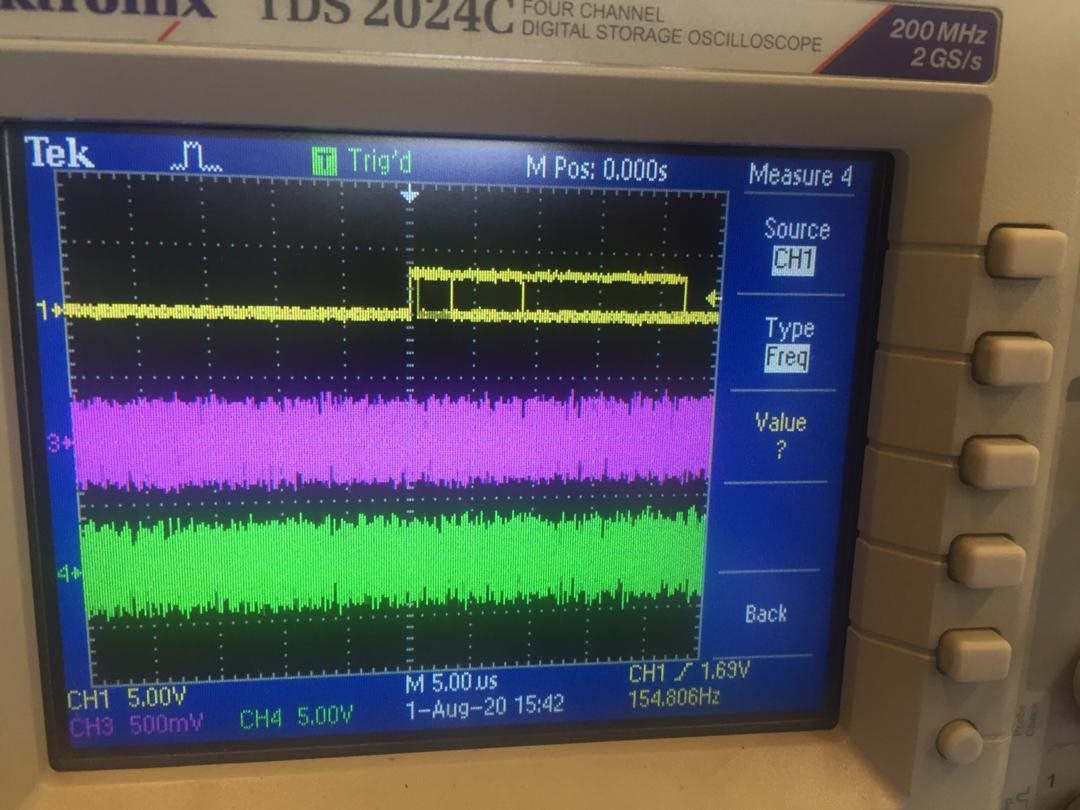

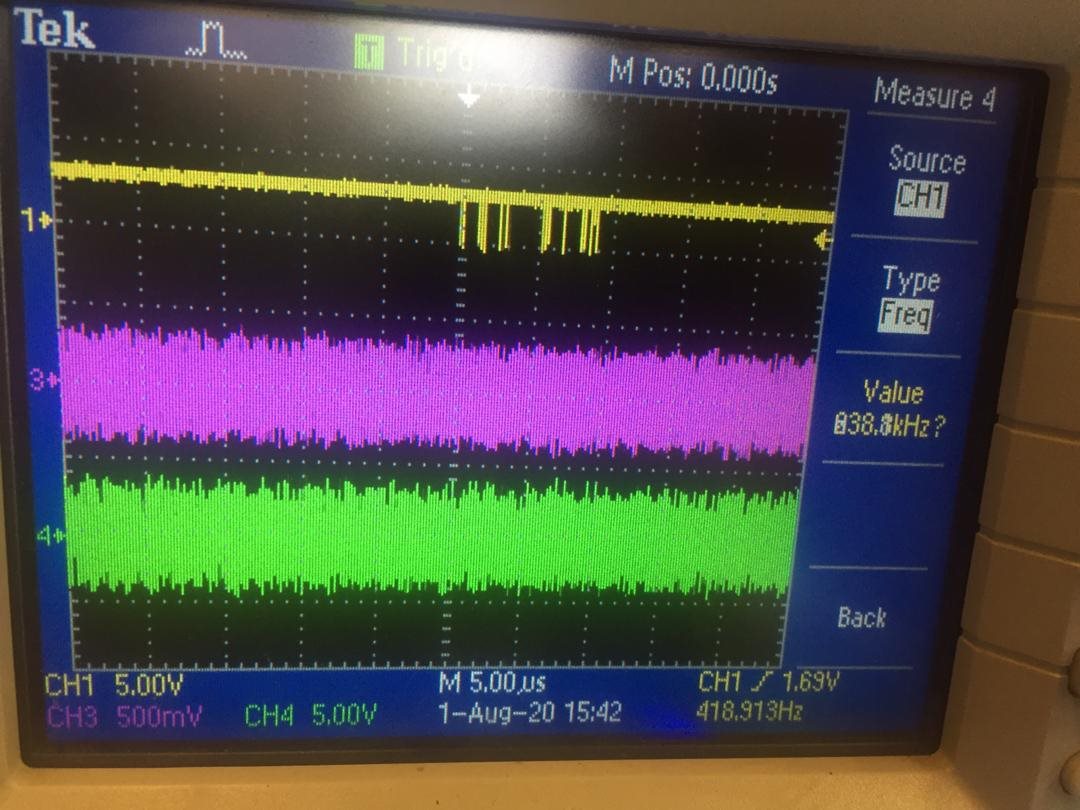

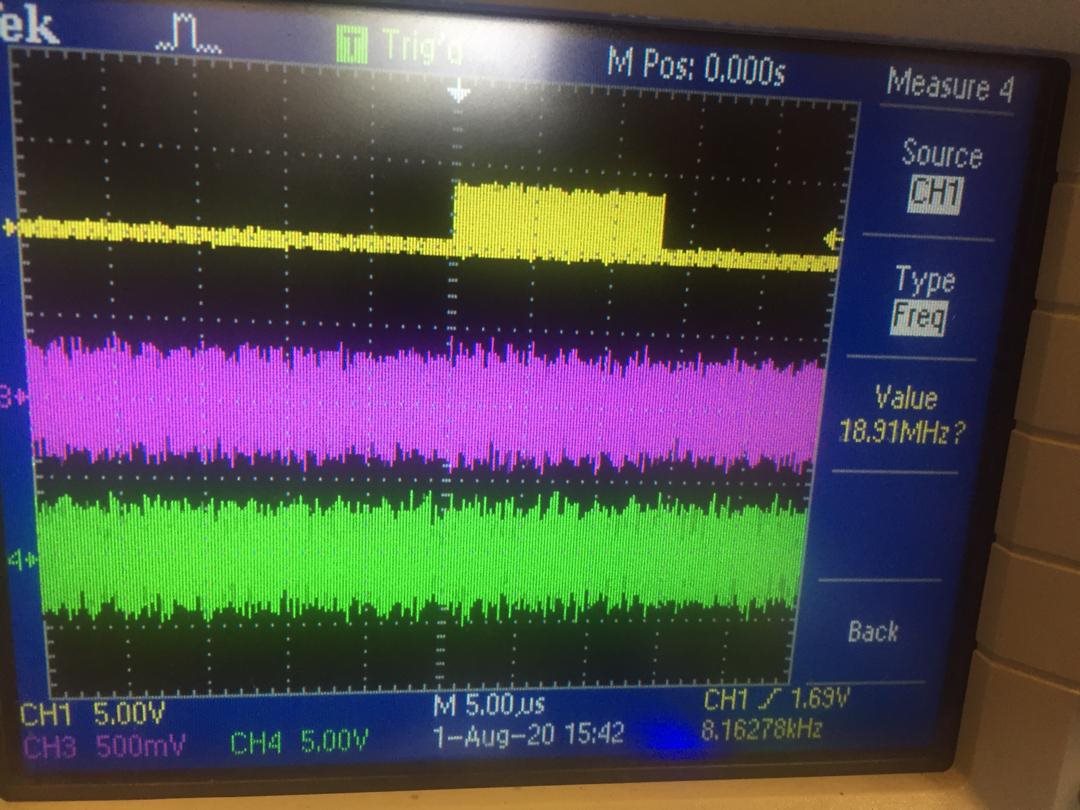

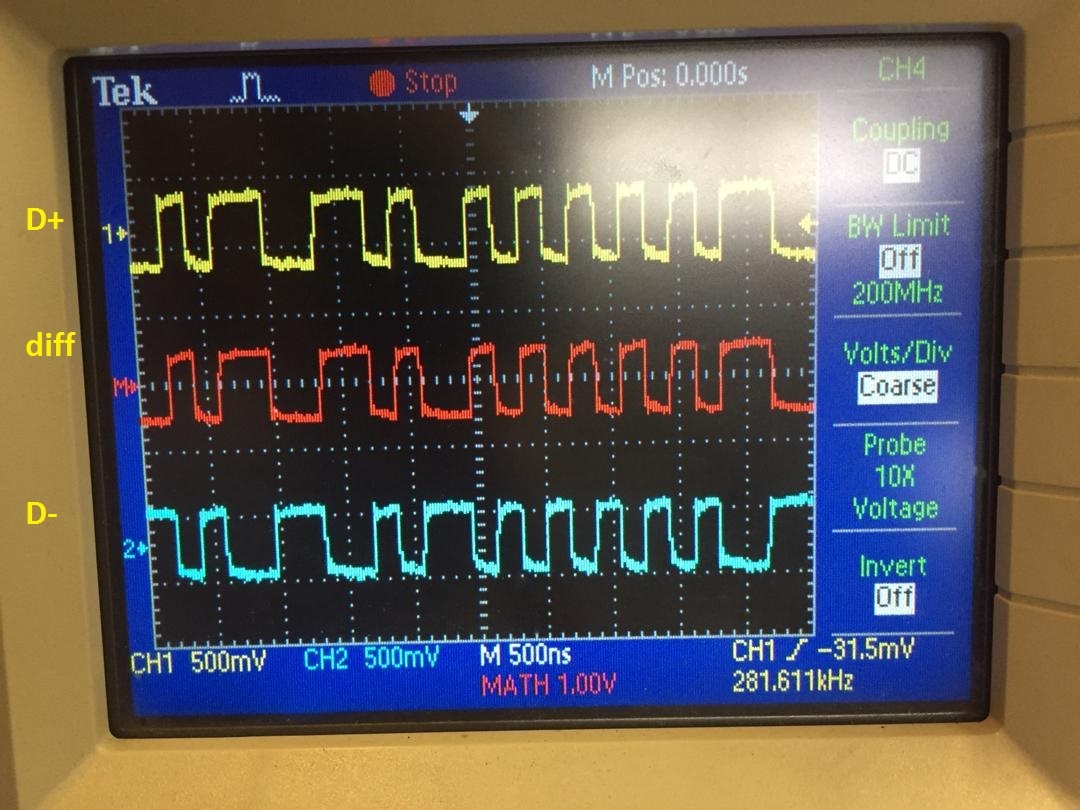

here is the link scope shot:

DS92LX1622 is not locked (LOCK=LOW and PASS=High)

and there is no PCLK or ROUT available on DSS92LX1622.

what is missing?