Hi,

I want to configure CSI Port 0 to generate a test pattern,but it cannot work well,I see the py script

# Set CSI Timing parameters for 400Mbps operation (both ports)

board.Ind_Acc_Write(0x0, 0x40, [0x83, 0x8D, 0x87, 0x87, 0x83, 0x86, 0x84, 0x86, 0x84], 9)

board.Ind_Acc_Write(0x0, 0x60, [0x83, 0x8D, 0x87, 0x87, 0x83, 0x86, 0x84, 0x86, 0x84], 9)

what's meaning of this。

how can i do it use i2cset?

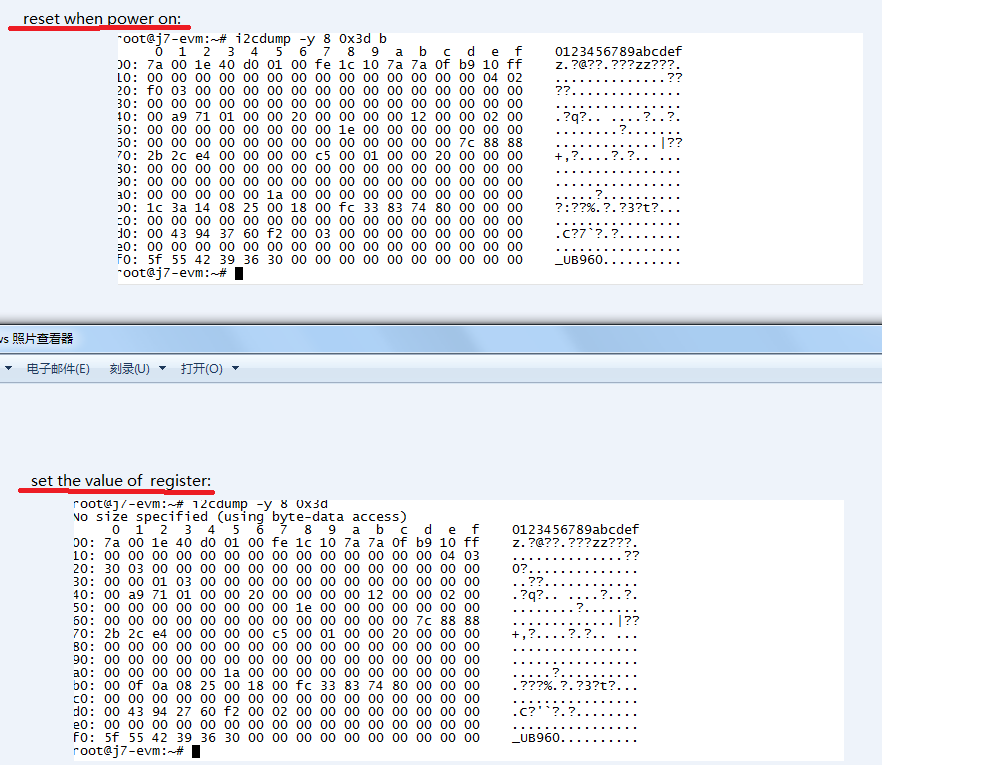

My setting is like the follow:

i2cset -y 8 0x3d 0x01 0x01

i2cset -y 8 0x3d 0x1F 0x03

# Set CSI Timing parameters for 400Mbps operation (both ports)

#board.Ind_Acc_Write(0x0, 0x40, [0x83, 0x8D, 0x87, 0x87, 0x83, 0x86, 0x84, 0x86, 0x84], 9)

#board.Ind_Acc_Write(0x0, 0x60, [0x83, 0x8D, 0x87, 0x87, 0x83, 0x86, 0x84, 0x86, 0x84], 9)

#

# CSI sel and CSI enable

i2cset -y 8 0x3d 0x32 0x01

msleep 500

i2cset -y 8 0x3d 0x33 0x03

msleep 500

# enable pat gen

i2cset -y 8 0x3d 0xB0 0x00

i2cset -y 8 0x3d 0xB1 0x01

i2cset -y 8 0x3d 0xB2 0x01

i2cset -y 8 0x3d 0xB1 0x02

i2cset -y 8 0x3d 0xB2 0x33

i2cset -y 8 0x3d 0xB1 0x03

i2cset -y 8 0x3d 0xB2 0x24

i2cset -y 8 0x3d 0xB1 0x04

i2cset -y 8 0x3d 0xB2 0x16

i2cset -y 8 0x3d 0xB1 0x05

i2cset -y 8 0x3d 0xB2 0x80

i2cset -y 8 0x3d 0xB1 0x06

i2cset -y 8 0x3d 0xB2 0x02

i2cset -y 8 0x3d 0xB1 0x07

i2cset -y 8 0x3d 0xB2 0xD0

i2cset -y 8 0x3d 0xB1 0x08

i2cset -y 8 0x3d 0xB2 0x04

i2cset -y 8 0x3d 0xB1 0x09

i2cset -y 8 0x3d 0xB2 0x38

i2cset -y 8 0x3d 0xB1 0x0a

i2cset -y 8 0x3d 0xB2 0x04

i2cset -y 8 0x3d 0xB1 0x0b

i2cset -y 8 0x3d 0xB2 0x65

i2cset -y 8 0x3d 0xB1 0x0c

i2cset -y 8 0x3d 0xB2 0x05

i2cset -y 8 0x3d 0xB1 0x0d

i2cset -y 8 0x3d 0xB2 0xc9

i2cset -y 8 0x3d 0xB1 0x0E

i2cset -y 8 0x3d 0xB2 0x21

i2cset -y 8 0x3d 0xB1 0x0F

i2cset -y 8 0x3d 0xB2 0x0A