Hi,

We are interfacing DP83867IRRGZ PHY with kintex ultrascale+ FPGA, XCKU5P with RGMII interface in one custom board. We are testing the 1GbE interface with Xilinx spartan 7 evaluation board as host. The RXMII RX path is verified by sending packets from Host to FPGA, and receiving packets from host to FPGA successfully. But when transmitting data from FPGA to host, the transmitted packets from the FPGA is dropped in host due to FCS error.

We probed the clock and TD signals and they are looks fine and the lines are proper length matched.

Suspecting some configuration mismatch with FPGA(TX) and PHY(RX).

We are using VCCIO bank voltage of FPGA as well as VDDIO voltage of PHY as 1.8V.

Is there any other configuration or settings we need to take care for PHY?

Kindly help here as soon as possible.

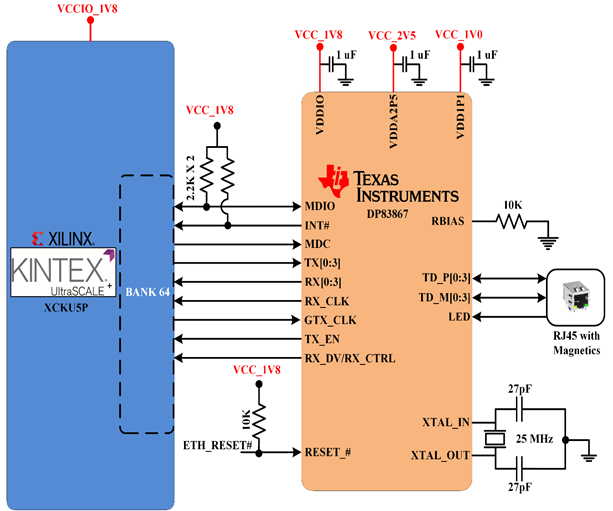

Our block diagram level implementation is as given below.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.